102 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 2: Shared Transceiver Features

Table 2-2 defines the attributes in the IBUFDS_GTXE1 software primitive that configure

the reference clock input.

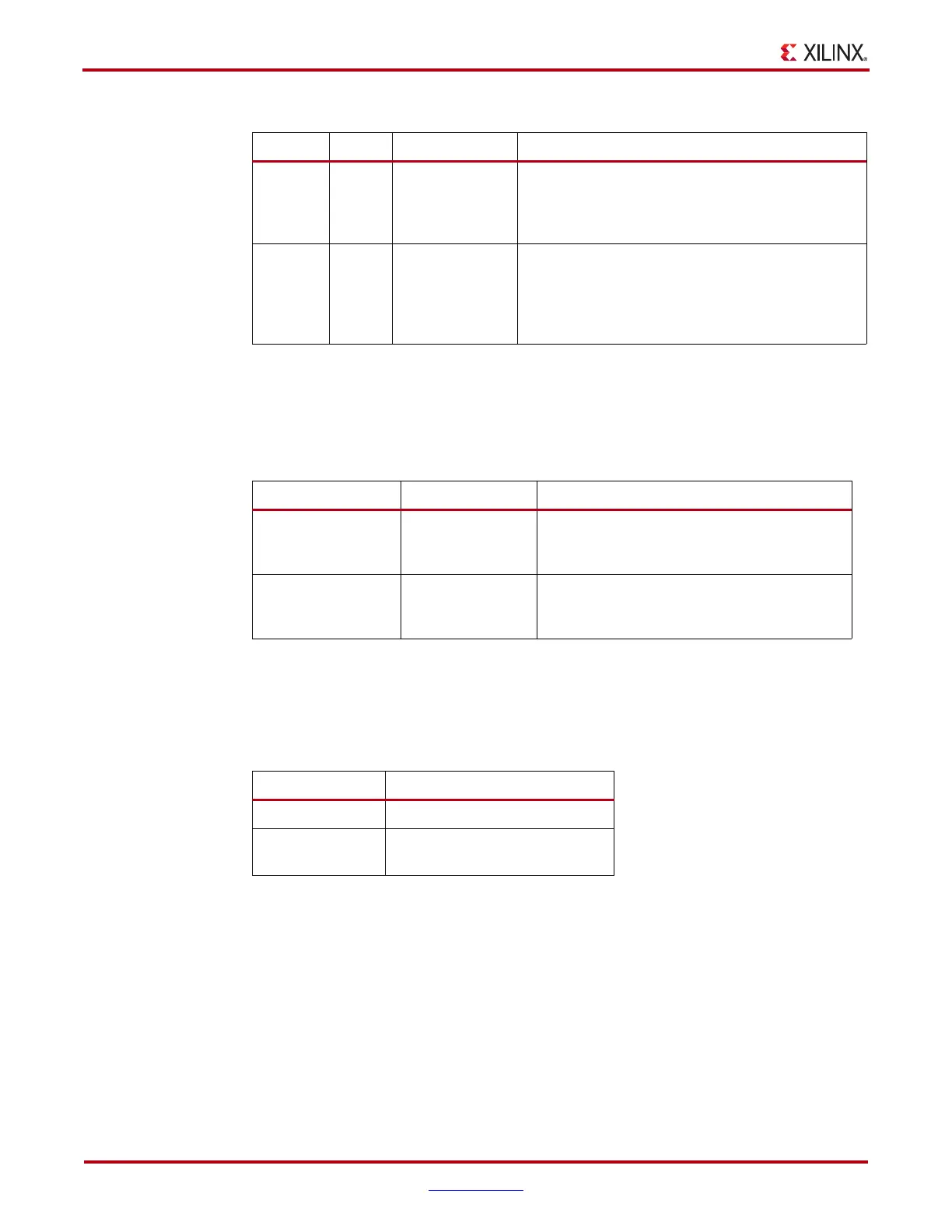

Use Modes: Reference Clock Termination

The reference clock input is to be externally AC coupled. Table 2-3 shows the pin and

attribute settings required to achieve this.

Reference Clock Selection

Functional Description

GTX transceivers provide several available reference clock inputs. Clock selection and

availability changed slightly across the first three generations of Virtex® FPGA

transceivers. The Virtex-6 FPGA GTX transceiver significantly enhances reference clock

capabilities by adding dedicated clock routing and multiplexer resources. Architecturally,

the concept of a Quad (or Q), contains a grouping of four GTXE1 primitives, two dedicated

reference clock pin pairs, and dedicated reference clock routing. The term Quad in this

O Out N/A This output drives the MGTREFCLKTX[0/1] and

MGTREFCLKRX[0/1] signals in the GTXE1

software primitive. Refer to Reference Clock

Selection, page 102 for more details.

ODIV2

(1)

Out N/A This output is a divide-by-2 version of the O signal

that can drive the MGTREFCLKTX[0/1] and

MGTREFCLKRX[0/1] signals in the GTXE1

software primitive. Refer to Reference Clock

Selection, page 102 for more details.

Notes:

1. The O and ODIV2 outputs are not phase matched to each other.

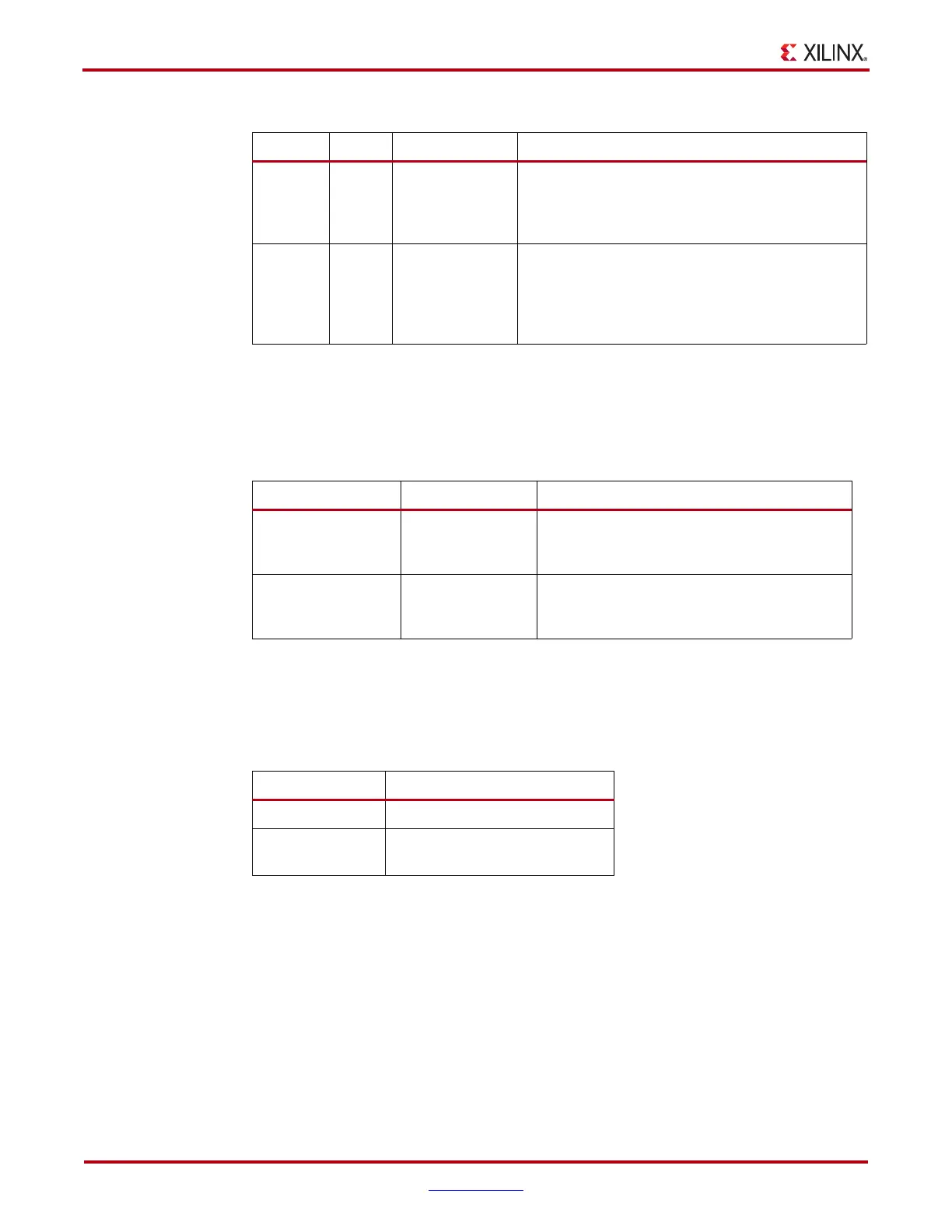

Table 2-2: Reference Clock Input Attributes (IBUFDS_GTXE1)

Attribute Type Description

CLKRCV_TRST Boolean RESTRICTED. This attribute switches in the

50 termination resistors into the signal path.

This attribute must always be set to TRUE.

CLKCM_CFG Boolean RESTRICTED. This attribute switches in the

termination voltage for the 50 termination.

This attribute must always be set to TRUE.

Table 2-1: Reference Clock Input Ports (IBUFDS_GTXE1) (Cont’d)

Port Dir Clock Domain Description

Table 2-3: Port and Attribute Settings

Input Type Settings

Ports CEB = 0

Attributes CLKRCV_TRST = TRUE

CLKCM_CFG = TRUE

Loading...

Loading...