Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 263

UG366 (v2.5) January 17, 2011

RX Initialization

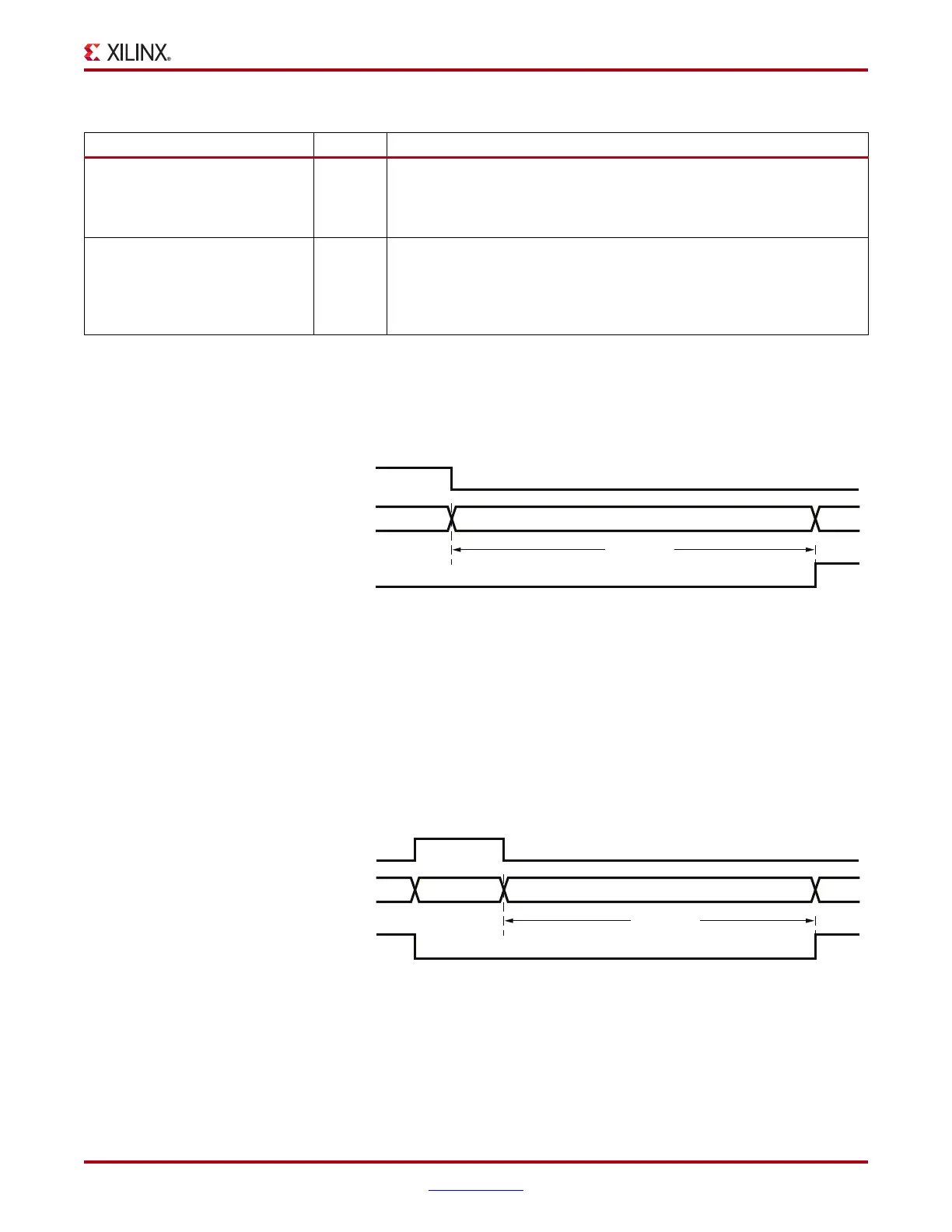

GTX RX Reset in Response to Completion of Configuration

Figure 4-50 shows the GTX RX reset following the completion of configuration of a

powered-up GTX transceiver. The same sequence is activated any time

RXPLLPOWERDOWN goes from High to Low during normal operation.

Note: The timing of the reset sequencer inside the GTX receiver depends on the frequency of an

internal clock and certain configuration attributes. The estimate given in Figure 4-50 assumes that

the frequency of the internal clock is 50 MHz with default values for the configuration attributes.

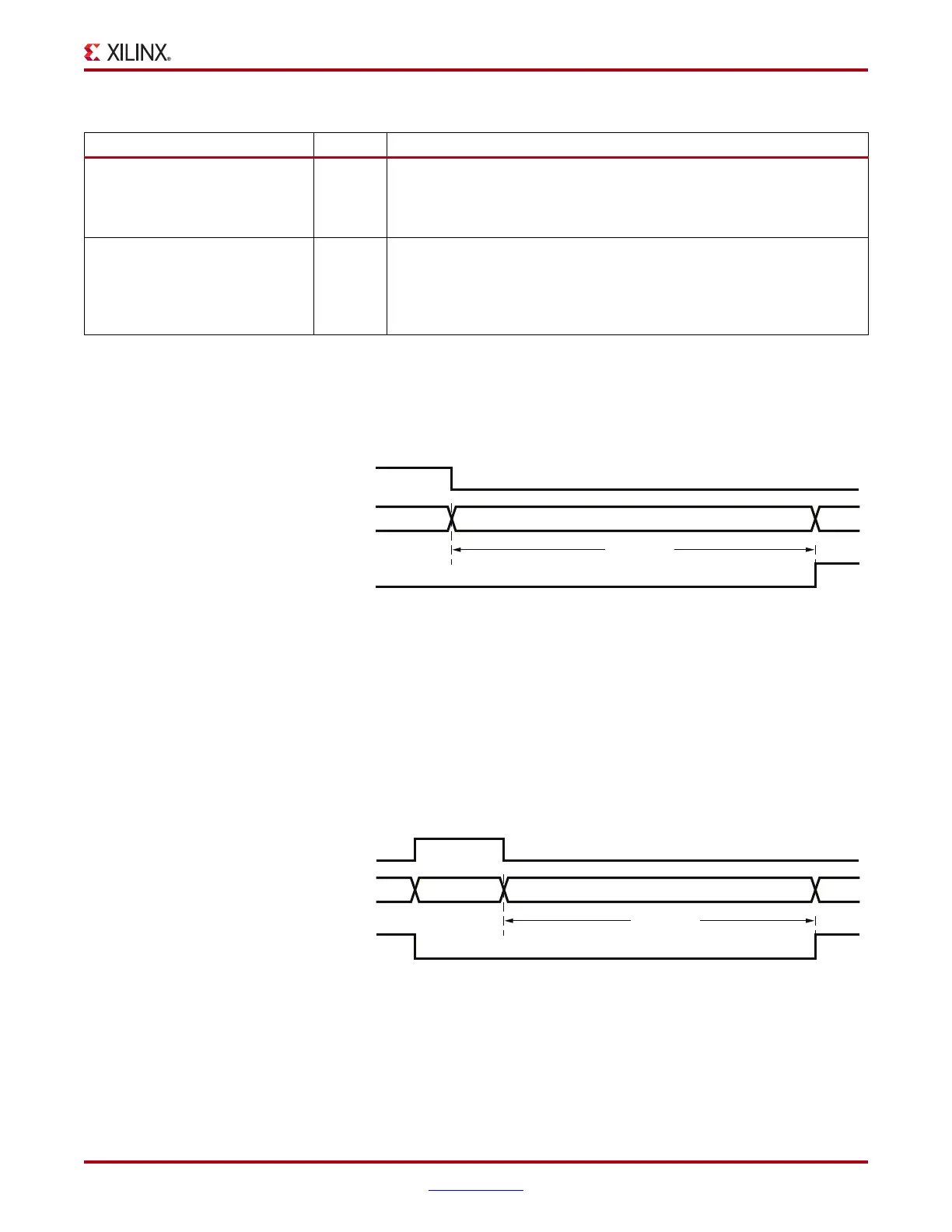

GTX RX Reset in Response to GTXRXRESET Pulse

Figure 4-51 is similar to Figure 4-50, showing the reset occurring in response to a pulse on

GTXRXRESET. GTXRXRESET acts as an asynchronous reset signal. The guideline for the

asynchronous GTXRXRESET pulse width is one period of the reference clock.

Note:

The timing of the reset sequencer inside the GTX RX depends on the frequency of an internal

clock and certain configuration attributes. The estimate given in Figure 4-51 assumes that the

frequency of the internal clock is 50 MHz with default values for the configuration attributes.

The entire GTX RX is affected by GTXRXRESET.

RX_IDLE_HI_CNT[3:0] 4-bit

Binary

Programmable counters used in association with resetting the RX elastic

buffer in response to the absence of valid data on the serial RX inputs.

Determines how long the serial RX inputs must remain in electrical idle

before the RX elastic buffer reset is asserted.

RX_IDLE_LO_CNT[3:0] 4-bit

Binary

Programmable counters associated with deasserting the reset condition

of the elastic buffer in response to the detection of valid data on the serial

RX inputs. Determines how long the serial RX inputs must have good

data (not be in electrical idle) before the RX elastic buffer reset is

deasserted.

Table 4-53: RX Initialization Attributes (Cont’d)

Attribute Type Description

X-Ref Target - Figure 4-50

Figure 4-50: Receiver Reset After Configuration

RXRESETDONE

RX Reset FSM

GSR

Wait Reset in Progress

~120 µs

Idle

UG366_c4_48_062209

X-Ref Target - Figure 4-51

Figure 4-51: Receiver Reset after GTXRXRESET Pulse

RXRESETDONE

RX Reset FSM

GTXRXRESET

Wait Reset in Progress

~120 µs

Idle

UG366_c4_47_062209

Idle

Loading...

Loading...