316 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Appendix C: Low Latency Design

GTX TX Latency

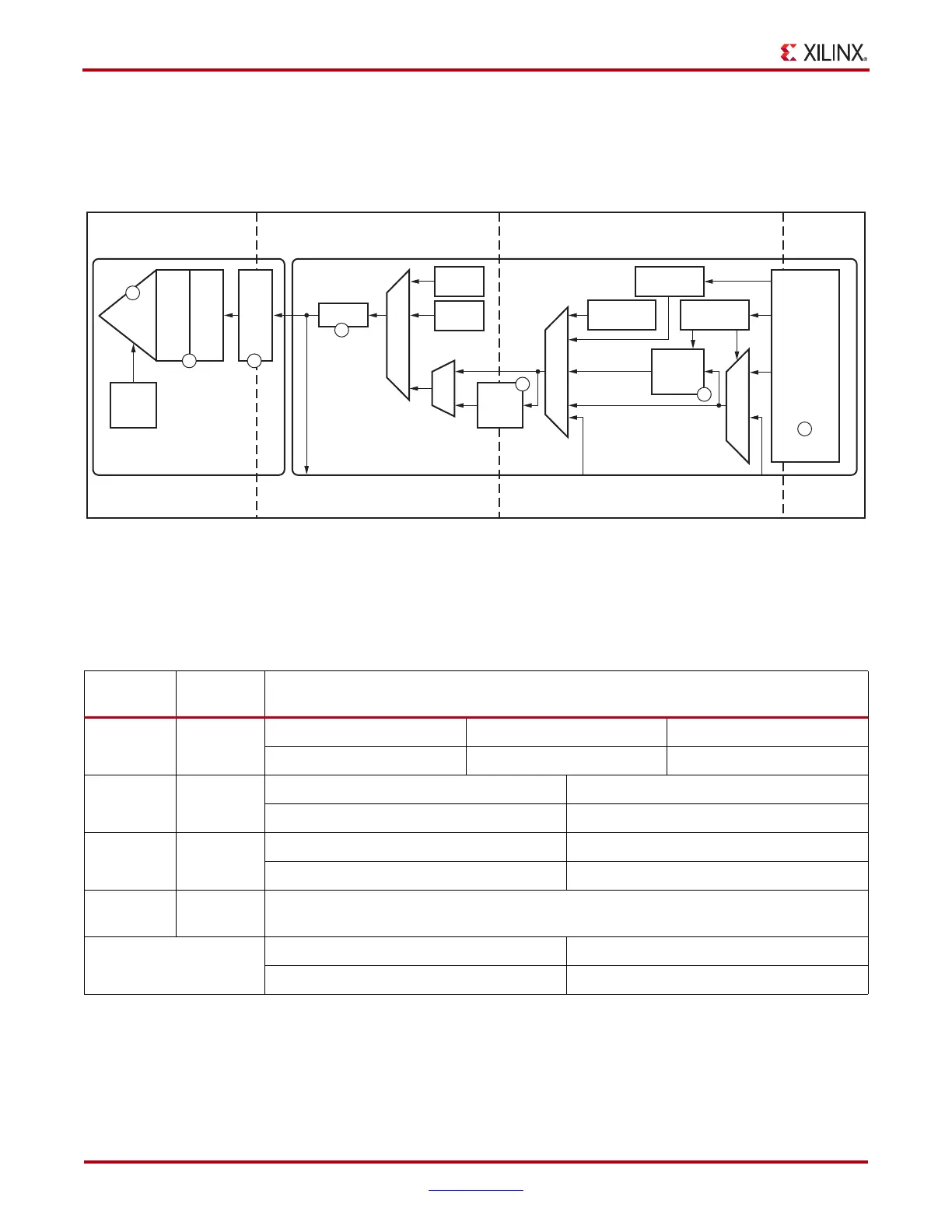

Figure C-2 shows a detailed block diagram of the GTX TX. Refer to TX Overview, page 127

for more details on the GTX TX blocks.

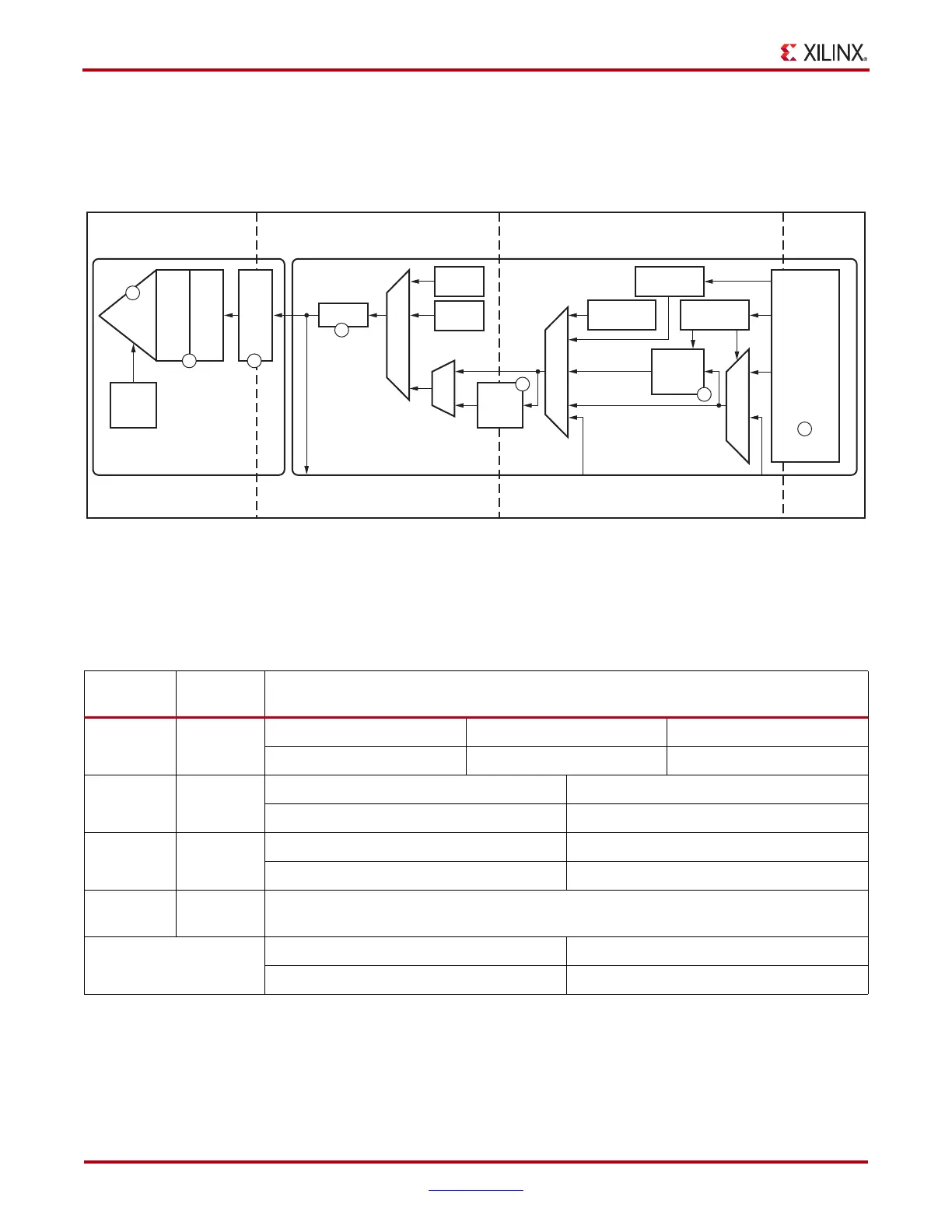

Table C-1 defines the latency for the specific functional blocks or group of functional blocks

of the transmitter section of the GTX transceiver. The values in the Block Number column

correspond to the circled numbers in Figure C-2.

X-Ref Target - Figure C-2

Figure C-2: GTX TX Block Diagram

FPGA TX

Interface

TX Gearbox

TX PIPE

Control

Pattern

Generator

PLL

TX

OOB

and

PCIe

TX

Driver

TX

Pre/

Post

Emp

PISOPolarity

PCIe

Beacon

SATA

OOB

Phase

Adjust

FIFO

8B/10B

Encoder

UG366_aC_02_110110

TX Serial Clock PMA Parallel Clock (XCLK) PCS Parallel Clock (TXUSRCLK)

FPGA Parallel

Clock

(TXUSRCLK2)

To RX Parallel Data

(Near-End PCS

Loopback)

From RX Parallel

Data (Far-End PMA

Loopback)

From RX Parallel

Data (Far-End PCS

Loopback)

TX PMA TX PCS

6

3

2

1

5

4

7

Table C-1: GTX TX Latency

Block

Number

Block

Name

TX Latency (TXUSRCLK)

1

FPGA TX

Interface

TX_DATA_WIDTH = 8/10 TX_DATA_WIDTH = 16/20 TX_DATA_WIDTH = 32/40

0.5 cycle 1 cycle 2 cycles

2

8B/10B

Encoder

TXENC8B10BUSE = 0 TXENC8B10BUSE = 1

0 cycles 1 cycle

3TX Buffer

TX_BUFFER_USE = FALSE TX_BUFFER_USE = TRUE

1 cycle 2 cycles

4+5+6+7

PMA +

Interface

2 cycles

Total TX Latency

Minimum Maximum

3.5 cycles 7 cycles

Loading...

Loading...