226 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

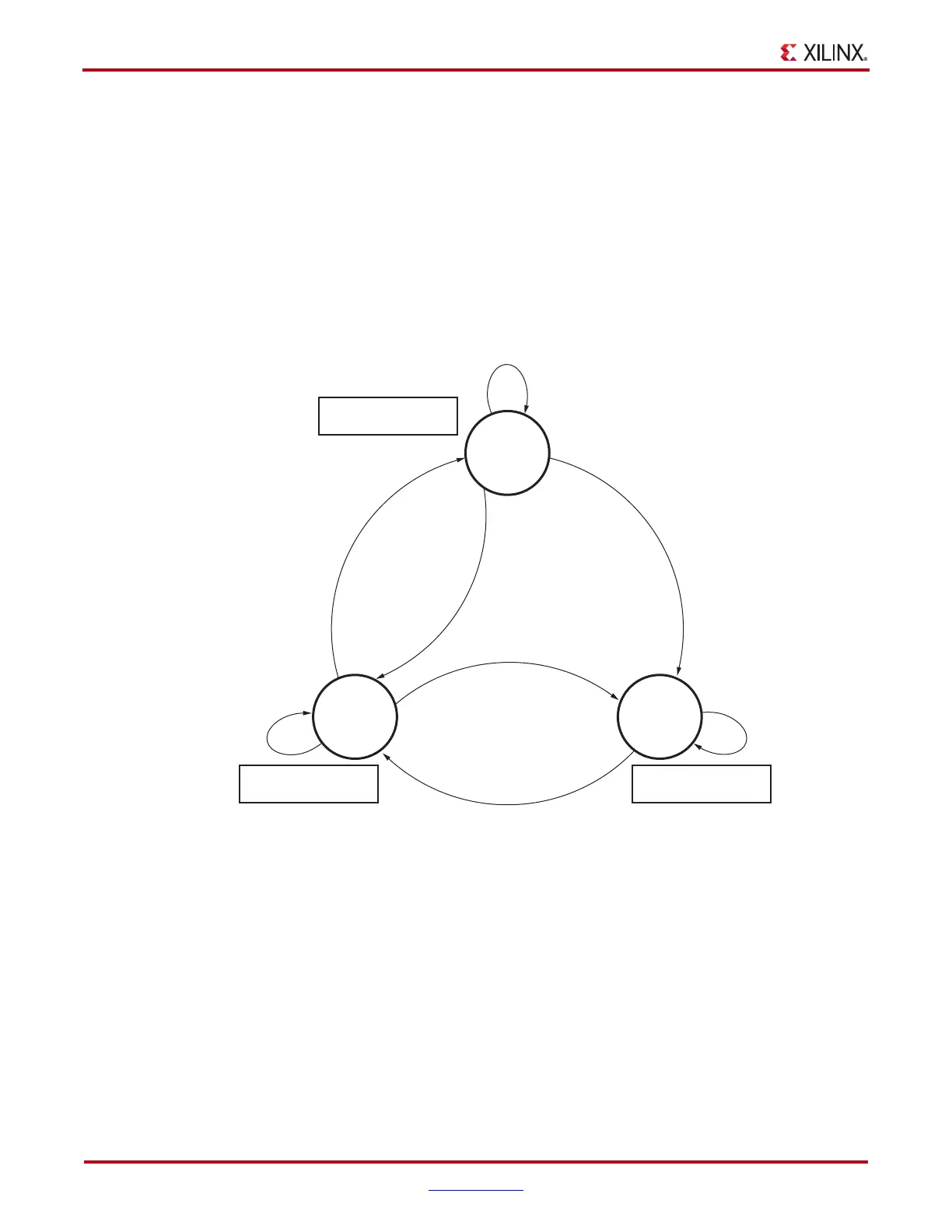

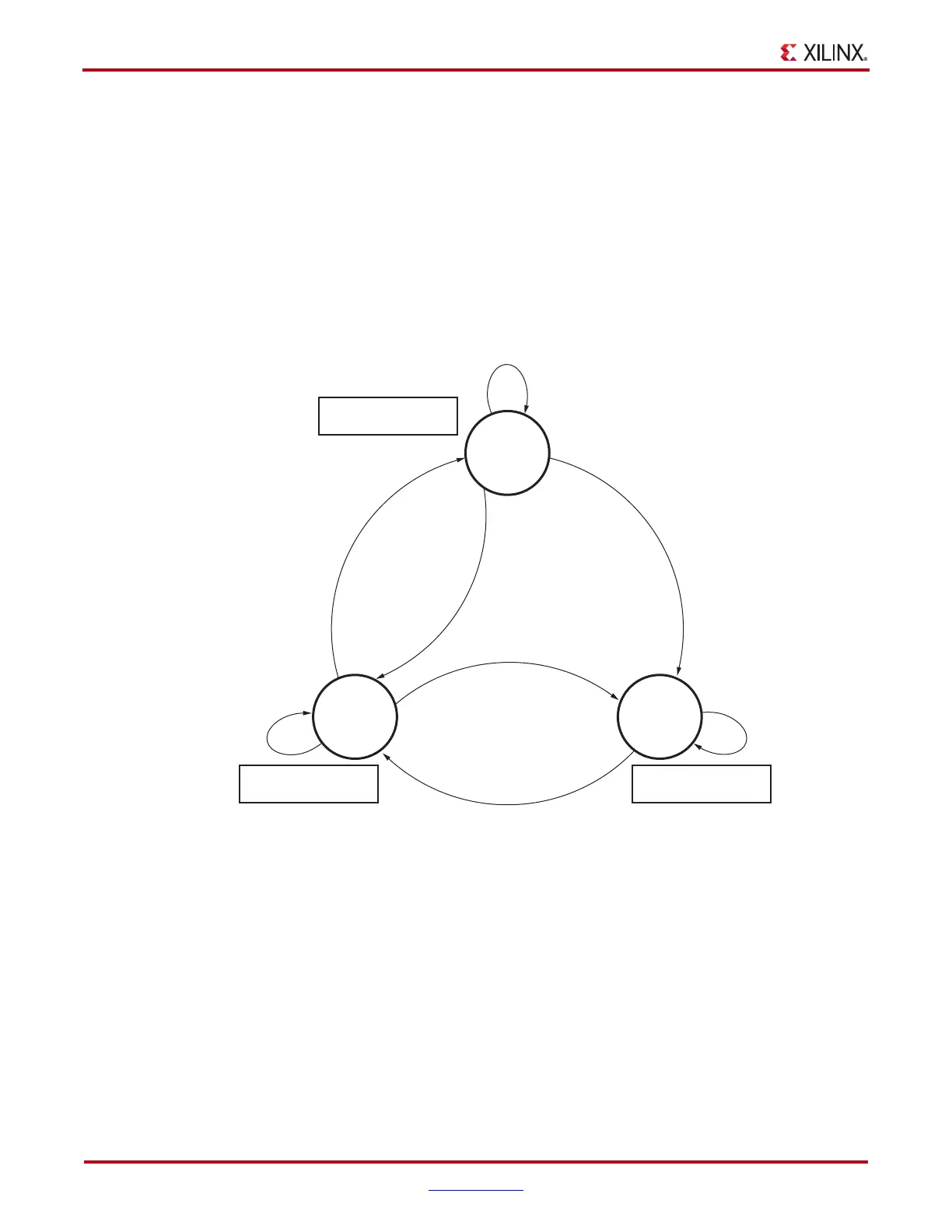

RX Loss-of-Sync State Machine

Functional Description

Several 8B/10B protocols make use of a standard Loss-of-Sync (LOS) state machine to

detect when the channel is malfunctioning. Each GTX receiver includes a LOS state

machine that can be activated for protocols requiring it. When the state machine is not

used, the LOS state machine's ports can be re-used to monitor the condition of incoming

data.

Figure 4-28 shows the standard LOS state machine, used in several 8B/10B protocols (for

example, XAUI) to detect problems in the incoming data stream.

To activate the LOS state machine in the GTX transceiver, RX_LOSS_OF_SYNC_FSM is set

to TRUE. While the state machine is active, the RXLOSSOFSYNC port presents its current

state.

If the LOS state machine is inactive (RX_LOSS_OF_SYNC_FSM = FALSE), the

RXLOSSOFSYNC port presents information about the received data. The

RXLOSSOFSYNC entry in Table 4-36 shows the meaning of the RXLOSSOFSYNC port in

this case.

The operation of the LOS state machine can be tuned using the RX_LOS_INVALID_INCR

and RX_LOS_THRESHOLD attributes. RX_LOS_THRESHOLD adjusts how sensitive the

LOS state machine is to bad characters (RX_LOS_THRESHOLD divided by

RX_LOS_INVALID_INCR) to change the machine from the SYNC_ACQUIRED state to the

X-Ref Target - Figure 4-28

Figure 4-28: LOS State Machine

00

01 10

No Comma Received

Count = RX_LOS_THRESHOLD

Count < RX_LOS_THRESHOLD/RX_LOS_INVALID_INCR

Channel Alignment

or

Comma Realignment

Invalid Data

Comma Received

UG366_c4_25_102910

Valid Data + 4 RXRECCLK Cycles

Valid Data + < 4 RXRECCLK Cycles

SYNC_ACQUIRED

RESYNC LOSS_OF_SYNC

Loading...

Loading...