136 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

For details about placement constraints and restrictions on clocking resources (MMCM,

BUFGCTRL, IBUFDS_GTXE1, BUFG, etc.), refer to the Virtex-6 FPGA Clocking Resources

User Guide.

TX Initialization

Functional Description

The GTX TX must be reset before it can be used. There are three ways to reset the GTX TX:

1. Power up and configure the FPGA. Power-up reset is covered in this section.

2. Drive the GTXTXRESET port High to trigger a full asynchronous reset of the GTX TX.

3. Assert one or more of the individual reset signals on the block to reset a specific

subcomponent of the transmitter. These resets are covered in detail in the sections for

each subcomponent (refer to Table 3-9, page 140 for a list of the available transmitter

resets).

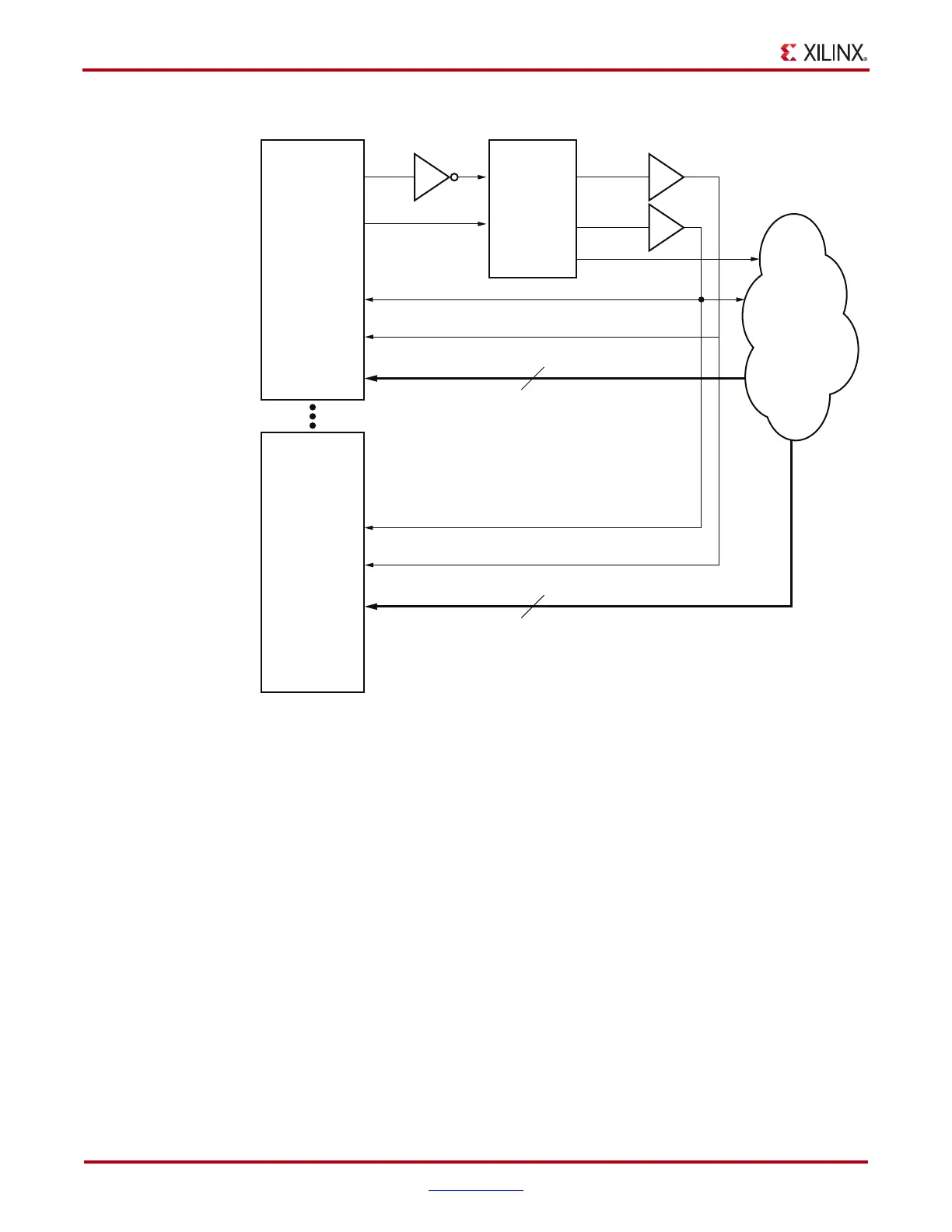

X-Ref Target - Figure 3-7

Figure 3-7: TXOUTCLK Driving More Than One GTX TX in 1-Byte Mode

GTX

Transceiver

TXPLLLKDET/

RXPLLLKDET

Design

in

FPGA

TXUSRCLK2

(1)

TXOUTCLK

RST

CLKIN

CLKOUT0

CLKOUT1

BUFG

BUFG

LOCKED

TXUSRCLK

(1)

MMCM

TXDATA (8 or 10 bits)

GTX

Transceiver

TXUSRCLK2

(1)

TXUSRCLK

(1)

TXDATA (8 or 10 bits)

Note 1: F

TXUSRCLK2

= 2 x F

TXUSRCLK

UG366_c3_22_061509

Loading...

Loading...