Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 125

UG366 (v2.5) January 17, 2011

ACJTAG

Table 2-17

defines the loopback

attributes.

ACJTAG

Functional Description

The Virtex-6 FPGA GTX transceiver supports ACJTAG, as specified by IEEE Std 1149.6. To

ensure reliable ACJTAG operation, the GTX RX expects the swing coming in to be

800 mV

PPD

(400 mV

PPSE

) or higher. In ACJTAG mode, the GTX TX swing is nominally

800 mV

PPD

. For JTAG clock operating frequencies specifically in ACJTAG mode, refer to

the Virtex-6 FPGA Data Sheet.

Dynamic Reconfiguration Port

Functional Description

The dynamic reconfiguration port (DRP) allows the dynamic change of parameters of the

GTXE1 primitive. The DRP interface is a processor-friendly synchronous interface with an

address bus (DADDR) and separated data buses for reading (DRPDO) and writing (DI)

configuration data to the GTXE1 primitive. An enable signal (DEN), a read/write signal

(DWE), and a ready/valid signal (DRDY) are the control signals that implement read and

write operations, indicate operation completion, or indicate the availability of data. Refer

to the Virtex-6 FPGA Configuration User Guide for detailed descriptions and timing

diagrams of the DRP operations. Refer to Appendix B, DRP Address Map of the GTX

Transceiver, for a DRP map of the GTX transceiver attributes.

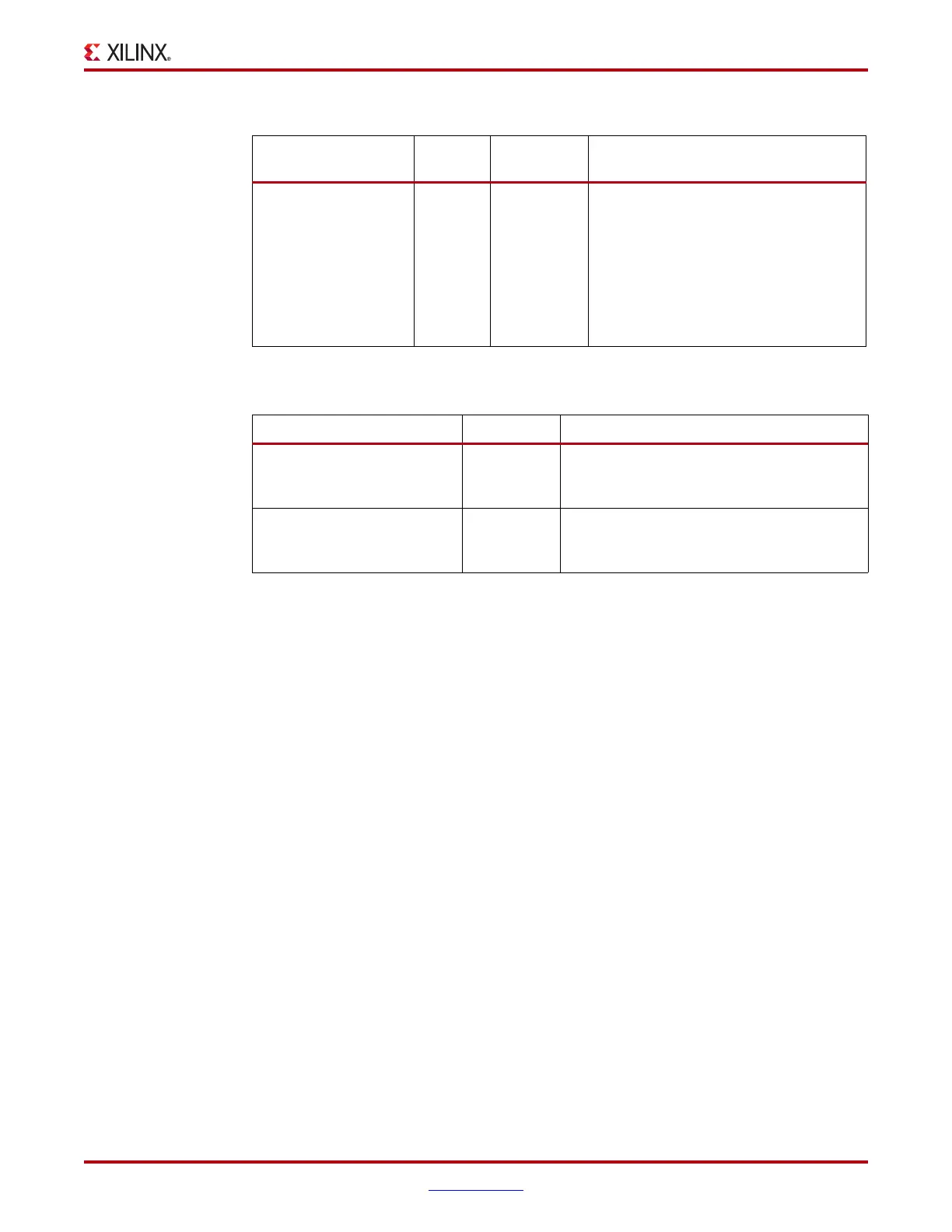

Table 2-16: Loopback Ports

Port Dir

Clock

Domain

Description

LOOPBACK[2:0] In Async 000: Normal operation

001: Near-End PCS Loopback

010: Near-End PMA Loopback

011: Reserved

100: Far-End PMA Loopback

101: Reserved

110: Far-End PCS Loopback

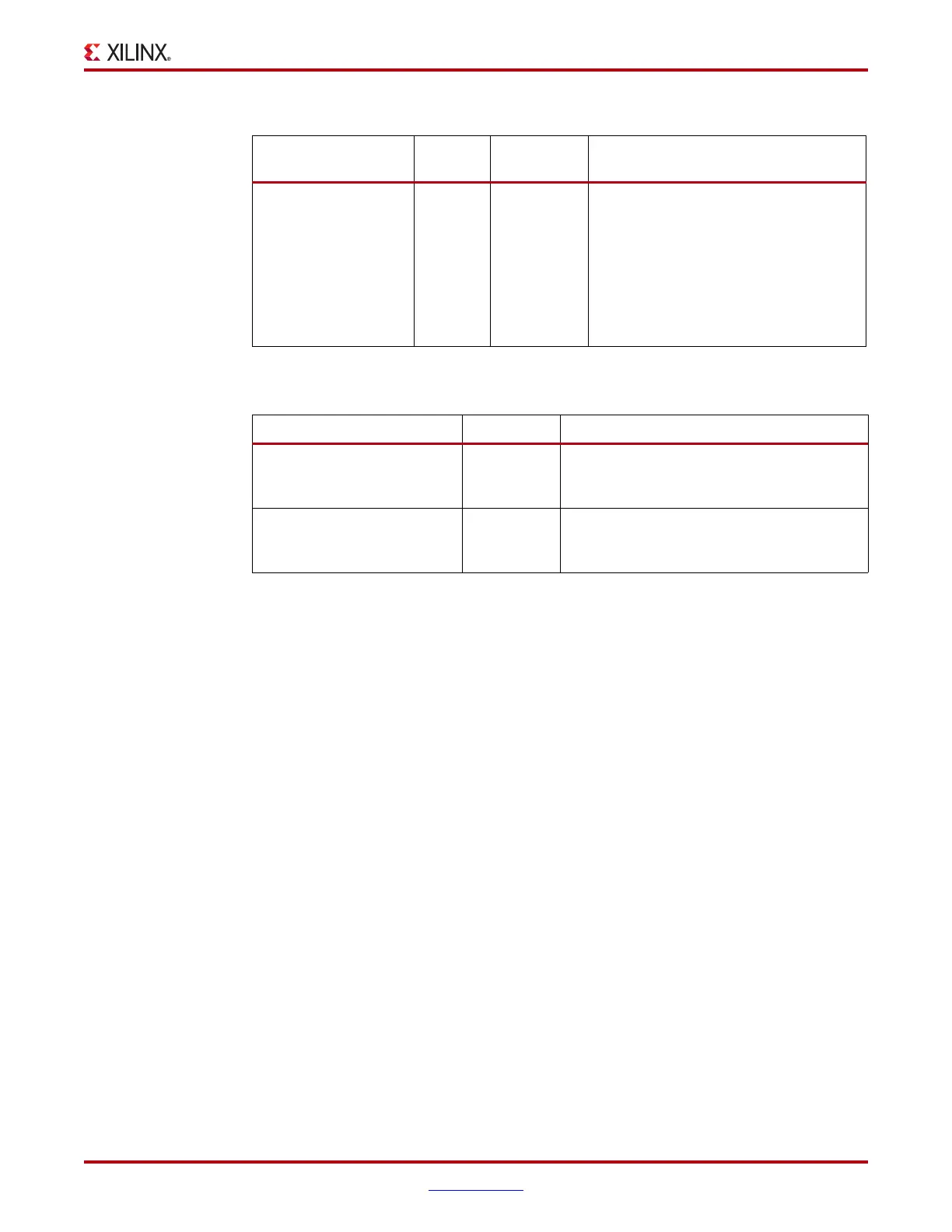

Table 2-17: Loopback Attributes

Port Type Description

TXDRIVE_LOOPBACK_HIZ Boolean Reserved. Use only recommended values

from the Virtex-6 FPGA GTX Transceiver

Wizard.

TXDRIVE_LOOPBACK_PD Boolean Reserved. Use only recommended values

from the Virtex-6 FPGA GTX Transceiver

Wizard.

Loading...

Loading...