240 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

Using the RX Elastic Buffer for Channel Bonding or Clock Correction

The RX elastic buffer is also used for clock correction (see RX Clock Correction) and

channel bonding (see RX Channel Bonding, page 247). Clock correction is used in cases

where PMACLK and RXUSRCLK are not frequency matched. Table 4-45 lists common

clock configurations and shows whether they require clock correction.

To use the RX elastic buffer for channel bonding or clock correction:

• Set RX_BUFFER_USE to TRUE.

• Reset the buffer whenever RXBUFSTATUS indicates an overflow or an underflow.

• The buffer can be reset using GTXRXRESET, RXRESET, or RXBUFRESET (see RX

Initialization, page 261).

RX Clock Correction

Functional Description

The RX elastic buffer has an additional benefit: it can tolerate frequency differences

between the XCLK and RXUSRCLK domains by performing clock correction. Clock

correction actively prevents the RX elastic buffer from getting too full or too empty by

deleting or replicating special idle characters in the data stream.

Figure 4-35 shows a conceptual view of clock correction.

RX_IDLE_LO_CNT 4-bit

Binary

Determines count value after which a deassertion of reset due to

RX_EN_IDLE_RESET_BUF is triggered after valid data once again present on

the RXP/RXN lines. Use the Virtex-6 FPGA GTX Transceiver Wizard default.

RX_XCLK_SEL String Selects the clock used to drive the RX parallel clock domain (XCLK).

“RXREC”: (default) XCLK domain driven by recovered clock from CDR.

When RX_OVERSAMPLE_MODE is TRUE, the recovered clock is sourced

from the oversampling block.

“RXUSR”: RXUSRCLK port drives RX parallel clock domain. Use this

mode when bypassing the RX elastic buffer.

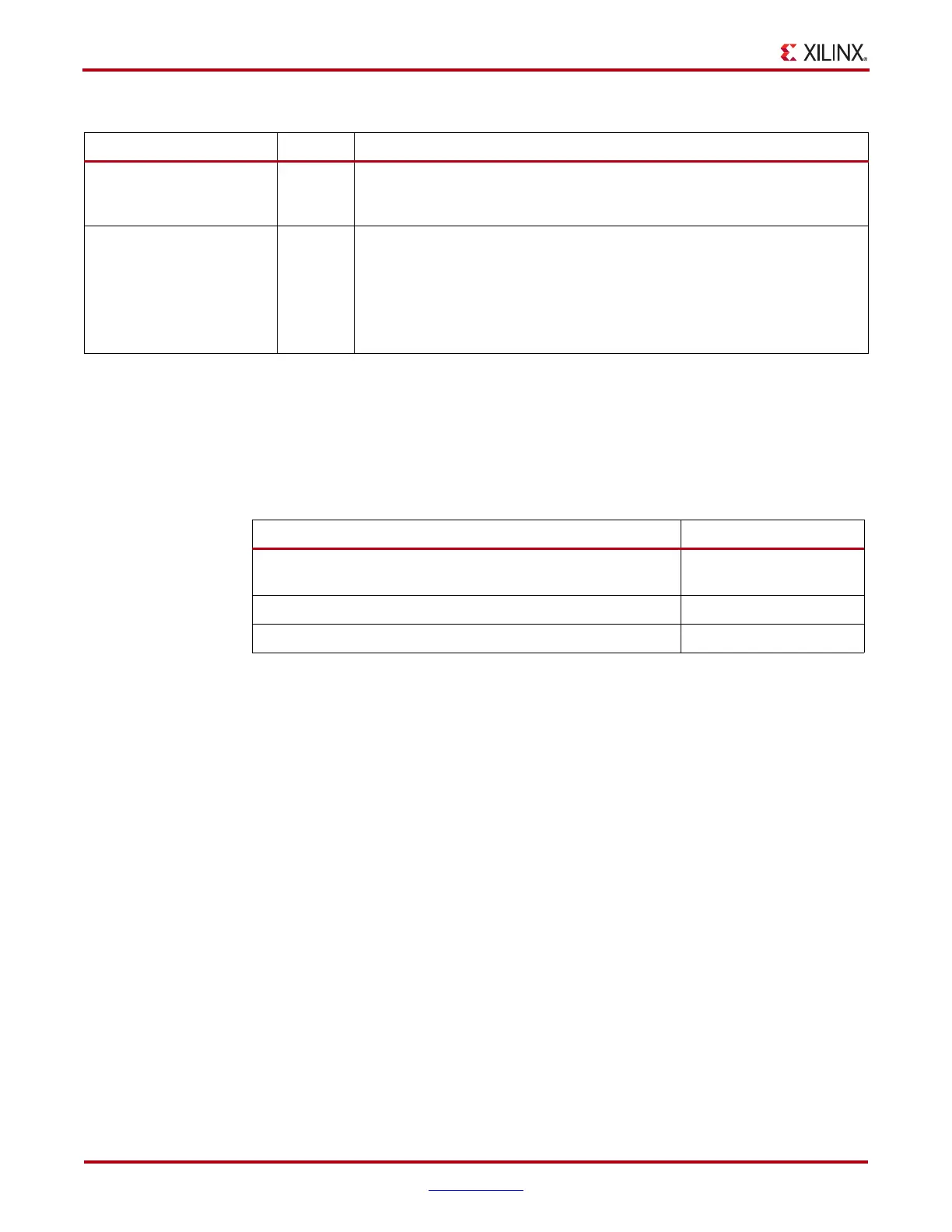

Table 4-44: RX Elastic Buffer Attributes (Cont’d)

Attribute Type Description

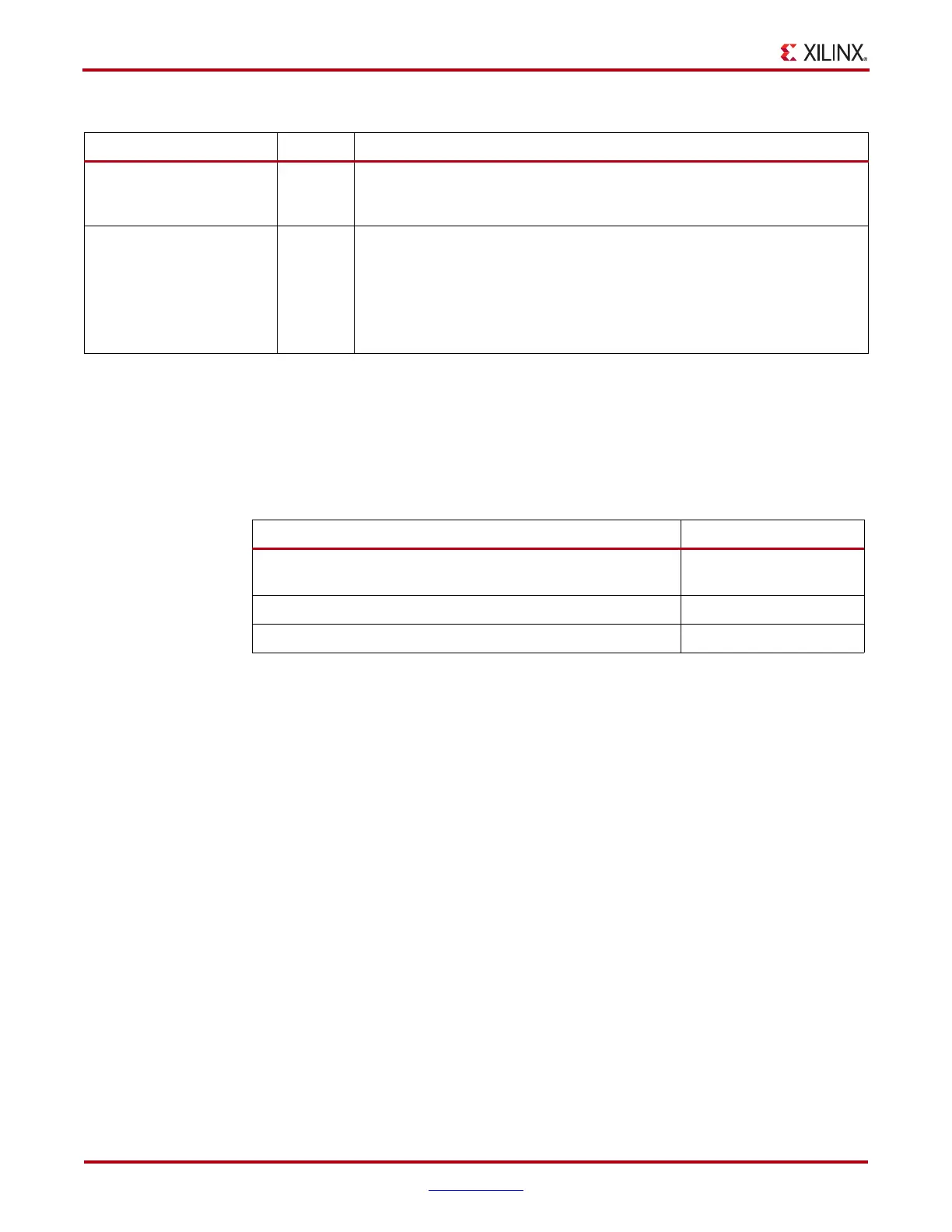

Table 4-45: Common Clock Configurations

Needs Clock Correction?

Synchronous System (both sides use same physical oscillator for

REFCLK)

No

Separate Reference Clocks, RX uses recovered clock No

Separate Reference Clocks, RX uses local clock Yes

Loading...

Loading...