260 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

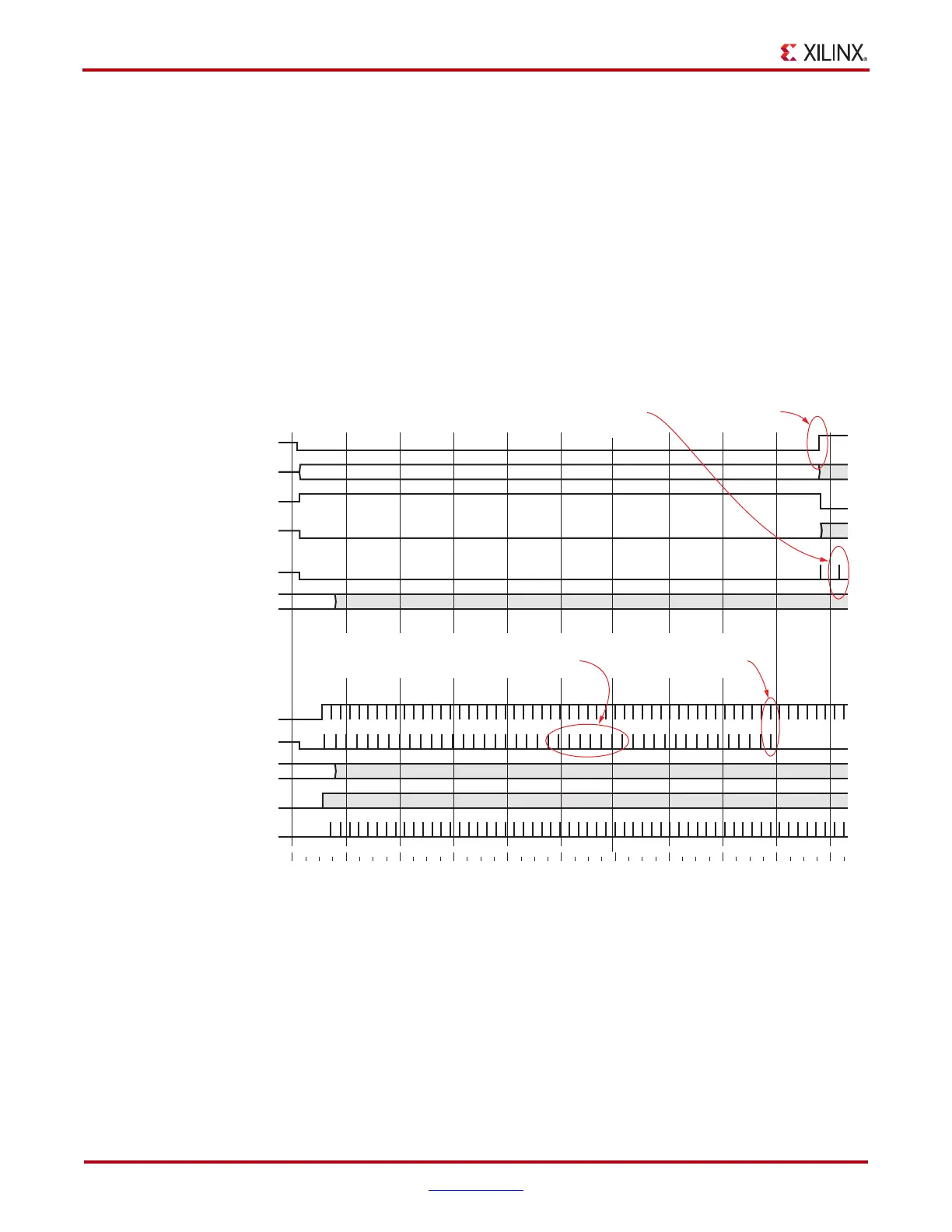

For the block synchronization state machine shown in Figure 4-47, sh_cnt_max and

sh_invalid_cnt_max are both constants that are set to 64 and 16, respectively. From the

VALID_SH state, if sh_cnt is less than the value sh_cnt_max and test_sh is High, the next

state is TEST_SH. If sh_cnt is equal to sh_cnt_max and sh_invalid_cnt equals 0, the next

state is GOOD_64 and from there block_lock is asserted. Then the process repeats again

and the counters are cleared to zeros. To achieve block lock, the state machine must receive

sh_cnt_max number of valid synchronization headers in a row without getting an invalid

synchronization header. However, when block lock is achieved, sh_invalid_cnt_max – 1

number of invalid synchronization headers can be received within sh_cnt_max number of

valid synchronization headers. Thus, once locked, it is harder to break lock.

Figure 4-48 shows a waveform of the block synchronization state machine asserting

RXGEARBOXSLIP numerous times because of invalid synchronization headers before

achieving data alignment.

X-Ref Target - Figure 4-48

Figure 4-48: RX Gearbox with Block Synchronization

UG366_c4_45_051509

Data alignment

achieved

Data check on

unscrambled data

block_sync_i

unscrambled_data_i

begin_r

track_data_r

start_of_packet_detected_r

RX_DATA

RXDATAVALID0

RXGEARBOXSLIP0

RXHEADER0

RXHEADERVALID0

RXSTA RTO FSEQ0

00000000

0

00000000

Slip data

alignment

Closely spaced slip pulses. State machine

asserts slip as soon as it sees bad header.

Loading...

Loading...