Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 259

UG366 (v2.5) January 17, 2011

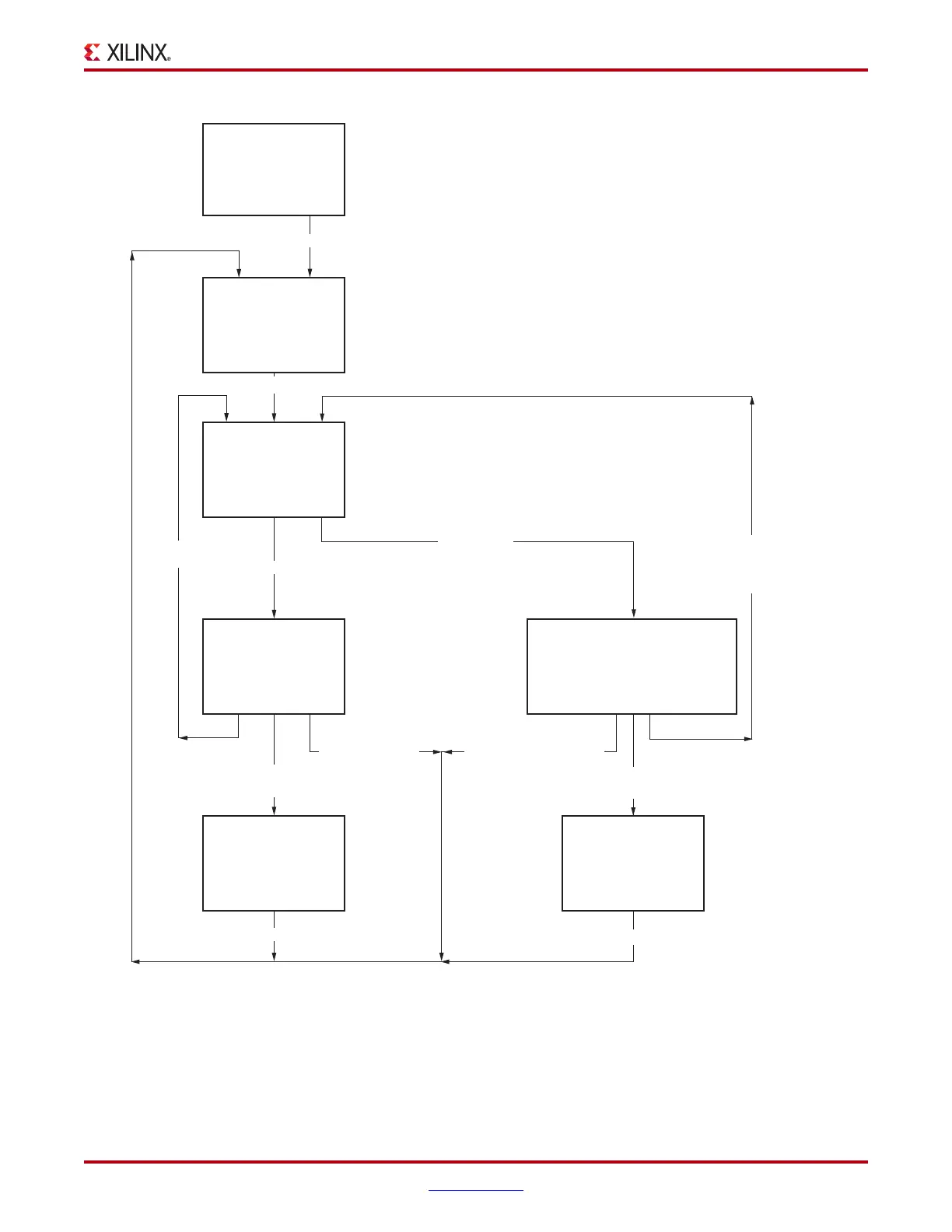

RX Gearbox

The state machine works by keeping track of valid and invalid synchronization headers.

Upon reset, block lock is deasserted, and the state is LOCK_INIT. The next state is

RESET_CNT where all counters are zeroed out. The synchronization header is analyzed in

the TEST_SH state. If the header is valid, sh_cnt is incremented in the VALID_SH state,

otherwise sh_count and sh_invalid_count are incremented in the INVALID_SH state.

X-Ref Target - Figure 4-47

Figure 4-47: Block Synchronization State Machine

LOCK_INIT

block_lock <= false

test_sh <= false

RESET_CNT

sh_cnt <= 0

sh_invalid_cnt <= 0

slip_done <= false

TEST_SH

test_sh <= false

VALID_SH

sh_cnt <= sh_cnt + 1

64_GOOD

block_lock <= true

SLIP

block_lock <= false

SLIP <= true

INVALID_SH

sh_cnt <= sh_cnt + 1

sh_invalid_cnt <= sh_invalid_cnt + 1

sh_cnt = 64 AND

sh_invalid_cnt = 0

sh_cnt = 64 AND

sh_invalid_cnt > 0

sh_cnt = 64 AND

sh_invalid_cnt < 16 AND

block_lock = true

sh_invalid_cnt = 16 OR

block_lock = false

slip_done = true

sh_valid = 0

Unconditional Transition

sh_valid = 1

test_sh = true AND

sh_cnt < 64

test_sh = 1

Unconditional Transition

test_sh = true AND

sh_cnt < 64 AND

sh_invalid_cnt < 16 AND

block_lock = true

UG366_c4_44_051509

Loading...

Loading...