118 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 2: Shared Transceiver Features

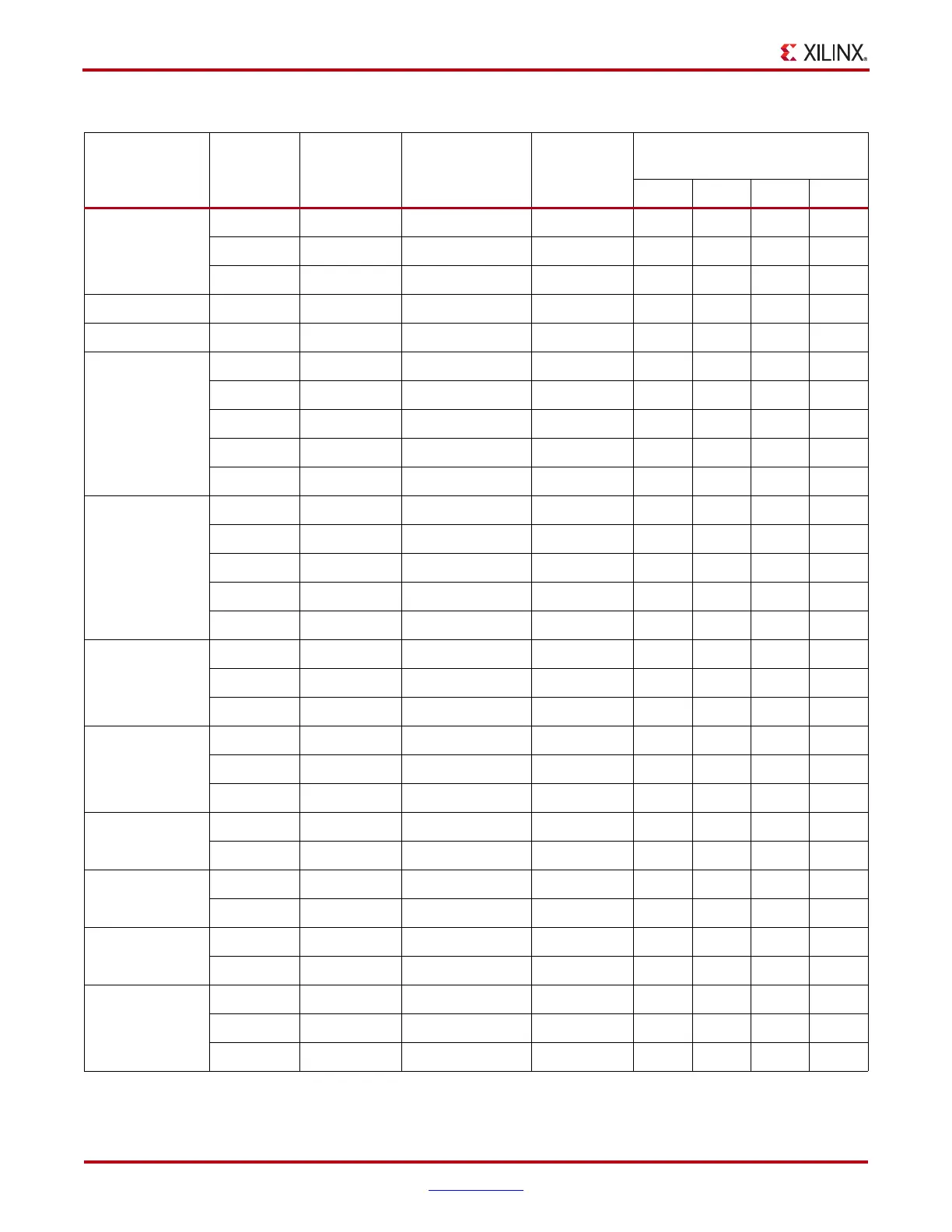

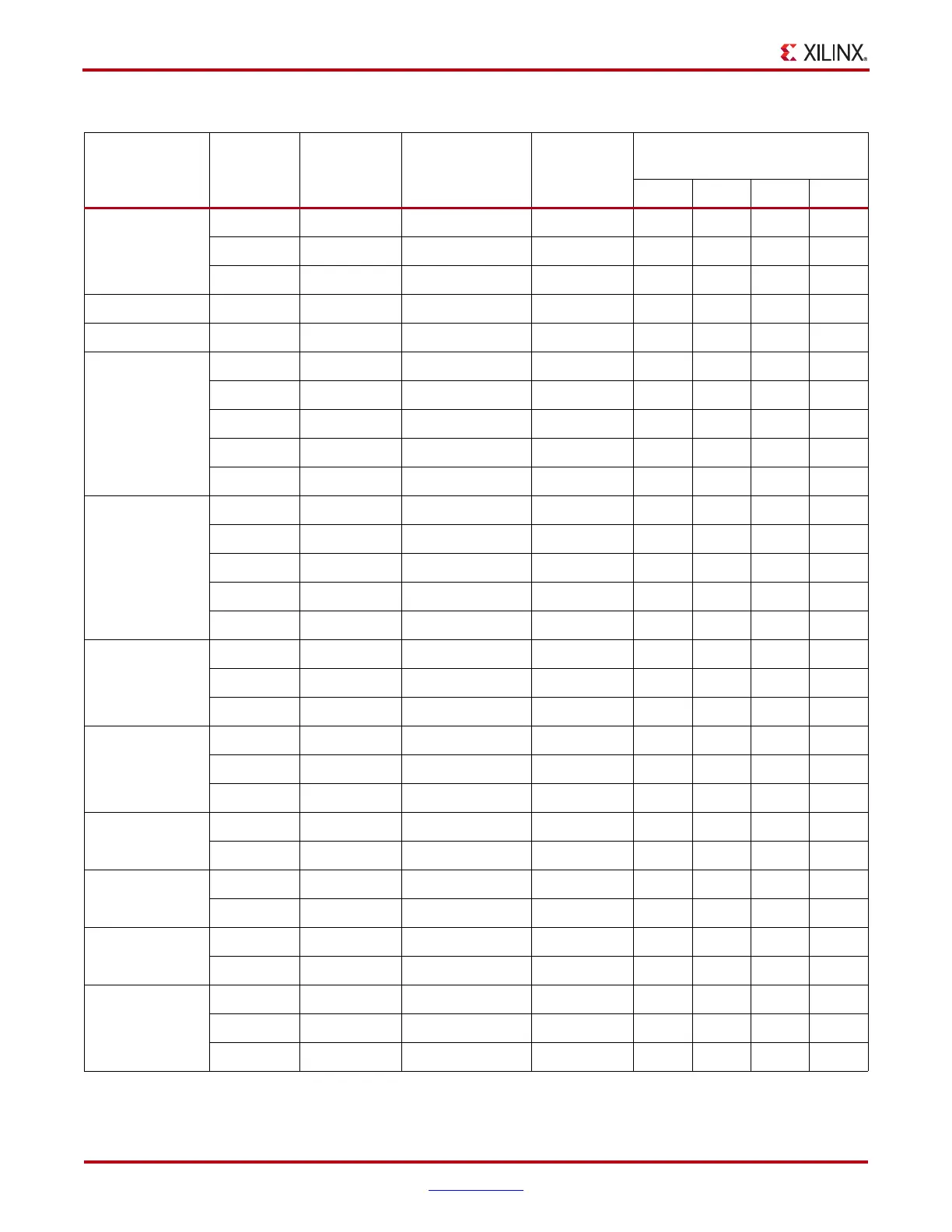

Fibre Channel

(Multi-Rate)

4.25 20b 2.125 212.5 5211

2.125 20b 2.125 212.5 5221

1.0625 20b 2.125 212.5 5241

XAUI 3.125 20b 1.5625 156.25 5211

GigE 1.25 20b 2.5 125 5441

Aurora

(Single Rate)

6.25 20b 3.125 312.5 5211

5 20b 2.5 250 5211

3.125 20b 1.5625 156.25 5211

2.5 20b 2.5 125 5421

1.25 20b 1.25 125 5221

Aurora

(Multi-Rate)

6.25 20b 3.125 312.5 5211

5 20b 2.5 312.5 4211

3.125 20b 3.125 312.5 5221

2.5 20b 2.5 312.5 4221

1.25 20b 2.5 312.5 4241

Serial RapidIO

(Single Rate)

3.125 20b 1.5625 156.25 5211

2.5 20b 2.5 125 5421

1.25 20b 2.5 125 5441

Serial RapidIO

(Multi-Rate)

3.125 20b 1.5625 156.25 5211

2.5 20b 2.5 156.25 4421

1.25 20b 2.5 156.25 4441

SATA

3 20b 1.5 150 5211

1.5 20b 1.5 150 5221

PCIe

Optimal Jitter

5 20b 2.5 250 5211

2.5 20b 2.5 125 5421

PCIe

100 MHz REFCLK

5 20b 2.5 100 5511

2.5 20b 2.5 100 5521

CPRI 1-4X

(Multi-Rate)

2.4576

20b 1.2288

122.88

5

211

1.2288

20b 1.2288

122.88

5

22

1

0.6144

20b 1.2288

122.88

5

241

Table 2-10: PLL Divider Settings for Common Protocols (Cont’d)

Standard

Line Rate

[Gb/s]

Internal Data

Width

[16b/20b]

PLL Frequency

[GHz]

REFCLK

(Typical)

[MHz]

Using Typical REFCLK

Frequency

N1 N2 D M

Loading...

Loading...