Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 119

UG366 (v2.5) January 17, 2011

PLL

Some protocols are shown twice as a single-rate configuration and a multi-rate

configuration. In single-rate configurations, only one line rate is required, and the

reference clock is optimized for that particular line rate. In multi-rate configurations, a

reference clock is selected for the highest line rate, and the appropriate dividers are

selected to support the lower line rates.

The general guidelines for the maximum, typical, and minimum frequencies for a given

protocol and line rate are:

• Maximum frequency is selected to use the minimum PLL multiplication ratio. This

option usually provides the highest jitter performance.

• Typical reference clock frequency is selected to limit the PLL multiplication to either

8 or 10 depending on the protocol.

• For lower line rate operation, the minimum frequency is selected to allow for a PLL

multiplication of 16 or 20.

• Performance impact needs to be carefully considered if a reference clock below the

typical recommended frequency is used. Refer to the Virtex-6 FPGA Data Sheet for the

minimum and maximum reference clock frequencies.

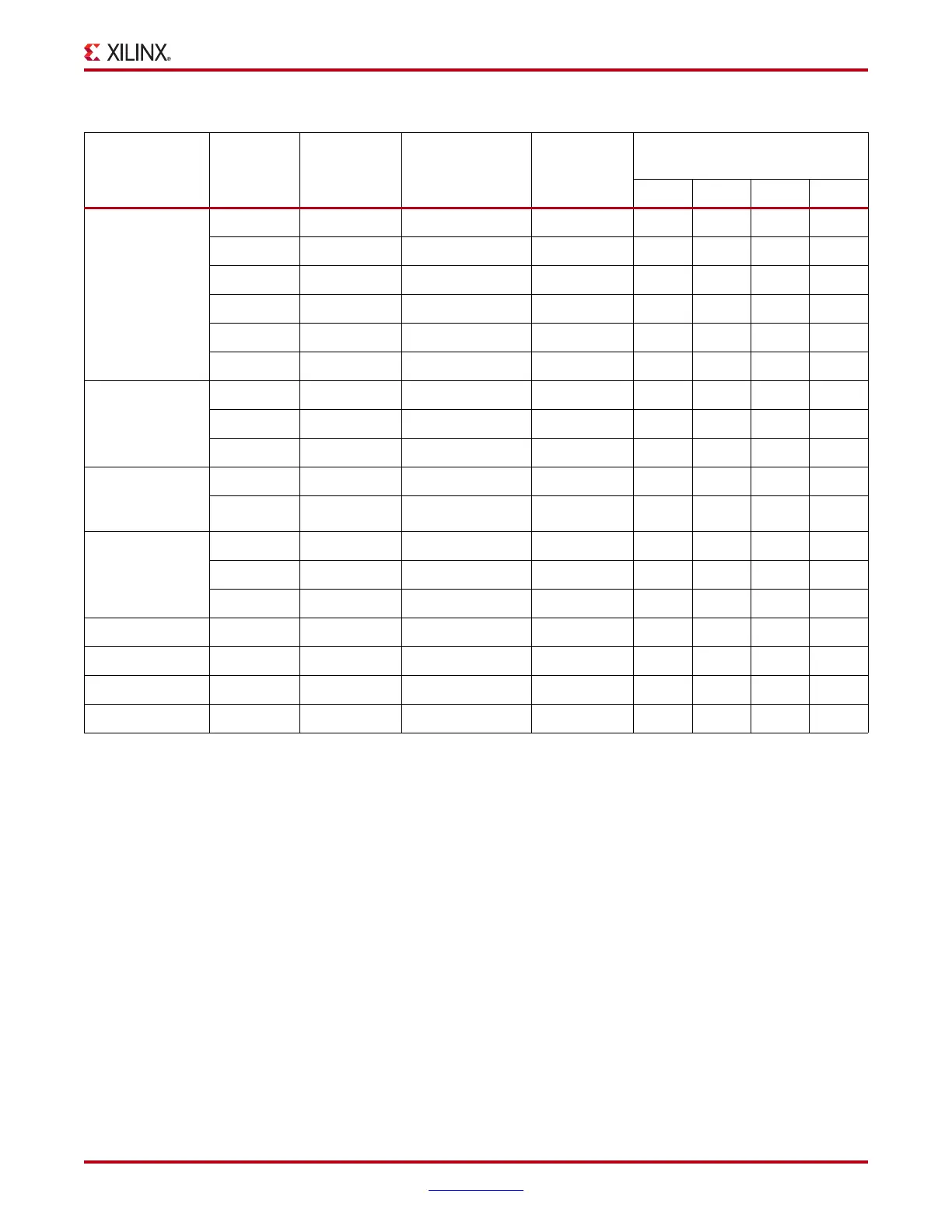

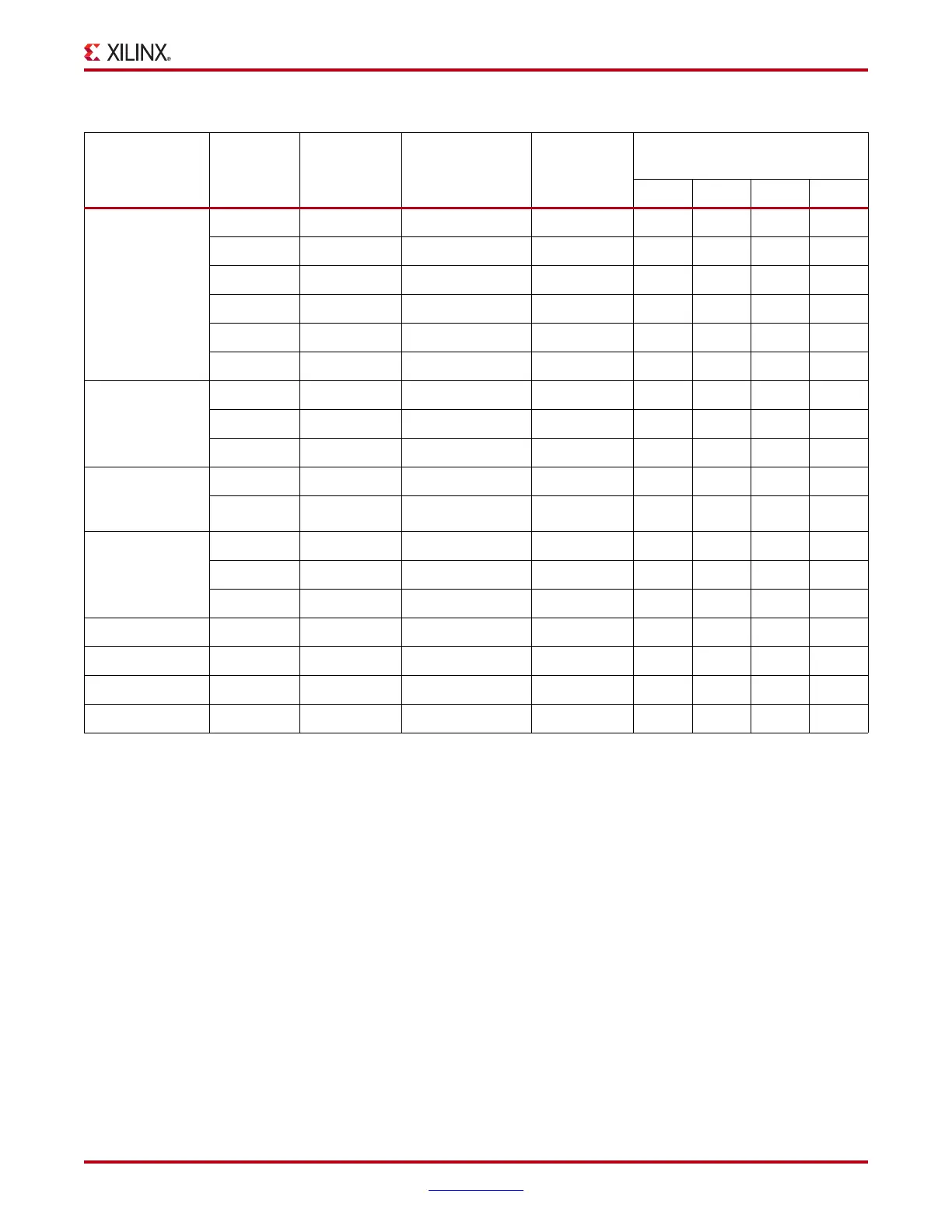

CPRI 1-10X

(Multi-Rate)

6.144

20b

3.072 307.2 5211

4.9152

20b

2.4576 307.2 4211

3.072 20b 3.072

307.2

5221

2.4576 20b

2.4576 307.2

4221

1.2288 20b

2.4576 307.2

4241

0.6144 20b

1.2288 307.2

4242

OBSAI

(Multi-Rate)

3.072 20b 1.536 153.6 5211

1.536 20b 1.536 153.6 5221

0.768 20b 1.536 153.6 5241

3G-SDI

HD-SDI

(Multi-Rate)

2.97 20b 1.485 148.5 5211

1.485 20b 1.485 148.5 5221

Interlaken

6.25 16b 3.125 312.5 5211

4.25 16b 2.125 212.5 5211

3.125 16b 3.125 156.25 5421

SFI-5 3.125 16b 3.125 195.3125 4421

OC-48

2.48832

16b

2.48832 155.52

4421

OC-12 0.62208 16b

1.24416

155.52 4241

OTU-1

2.666057

16b

2.666057

166.6286 4421

Table 2-10: PLL Divider Settings for Common Protocols (Cont’d)

Standard

Line Rate

[Gb/s]

Internal Data

Width

[16b/20b]

PLL Frequency

[GHz]

REFCLK

(Typical)

[MHz]

Using Typical REFCLK

Frequency

N1 N2 D M

Loading...

Loading...