152 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

The sequence of transmitting data for the internal sequence counter mode is:

1. Hold TXSTARTSEQ Low.

2. Assert TXRESET and wait until the reset cycle is completed.

3. TXGEARBOXREADY goes High.

4. During reset, place the appropriate header data on TXHEADER and the initial data on

TXDATA. This state can be held indefinitely in readiness for data transmission.

5. Drive TXSTARTSEQ High and place the first valid header information on TXHEADER

and data on TXDATA.

6. Continue to drive header information and data until TXGEARBOXREADY goes Low.

7. When TXGEARBOXREADY goes Low, drive the last 2 (or 4) bytes of data and the

header information (4-byte input mode).

8. Hold the data pipeline for four bytes of data (one TXUSRCLK2 cycle for a 4-byte input

or two TXUSRCLK2 cycles for a 2-byte input).

9. On the next TXUSRCLK2 cycle, drive data on the TXDATA inputs.

TXGEARBOXREADY is asserted High on the previous TXUSRCLK2 cycle.

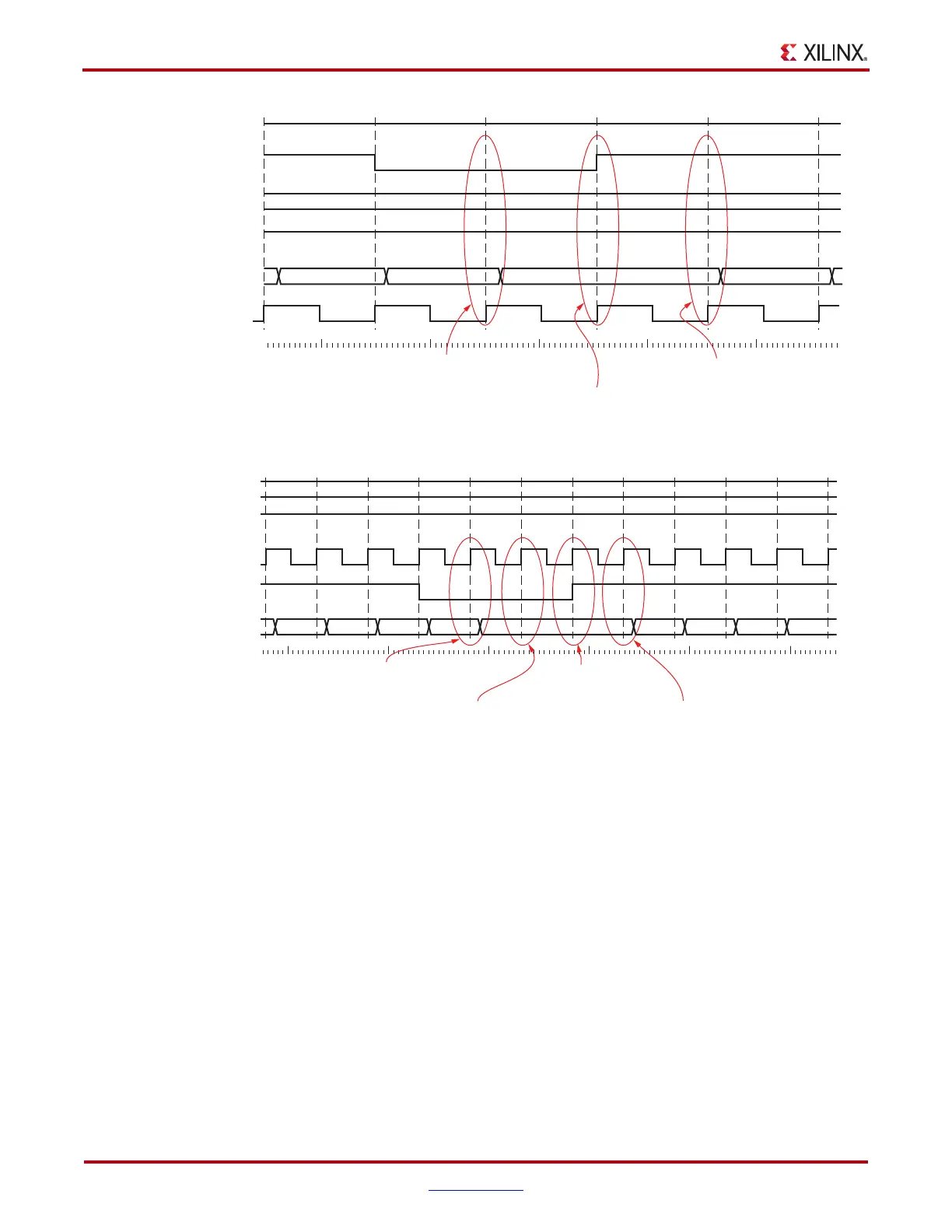

X-Ref Target - Figure 3-18

Figure 3-18: TX Gearbox Internal Sequence Mode, 4-Byte Interface, 64B/67B

UG366_c3_8_051509

81300de0 18c72cde 19928750 80209e96

GEARBOXREADY Low

Data still taken on this cycle.

GEARBOXREADY Low

Data not latched by Gearbox.

GEARBOXREADY High

Data latched by Gearbox.

1

TXUSRCLK20

TXGEARBOXREADY0

TXDATA0

TXSTA RT SEQ0

TXHEADER

RESETDONE0

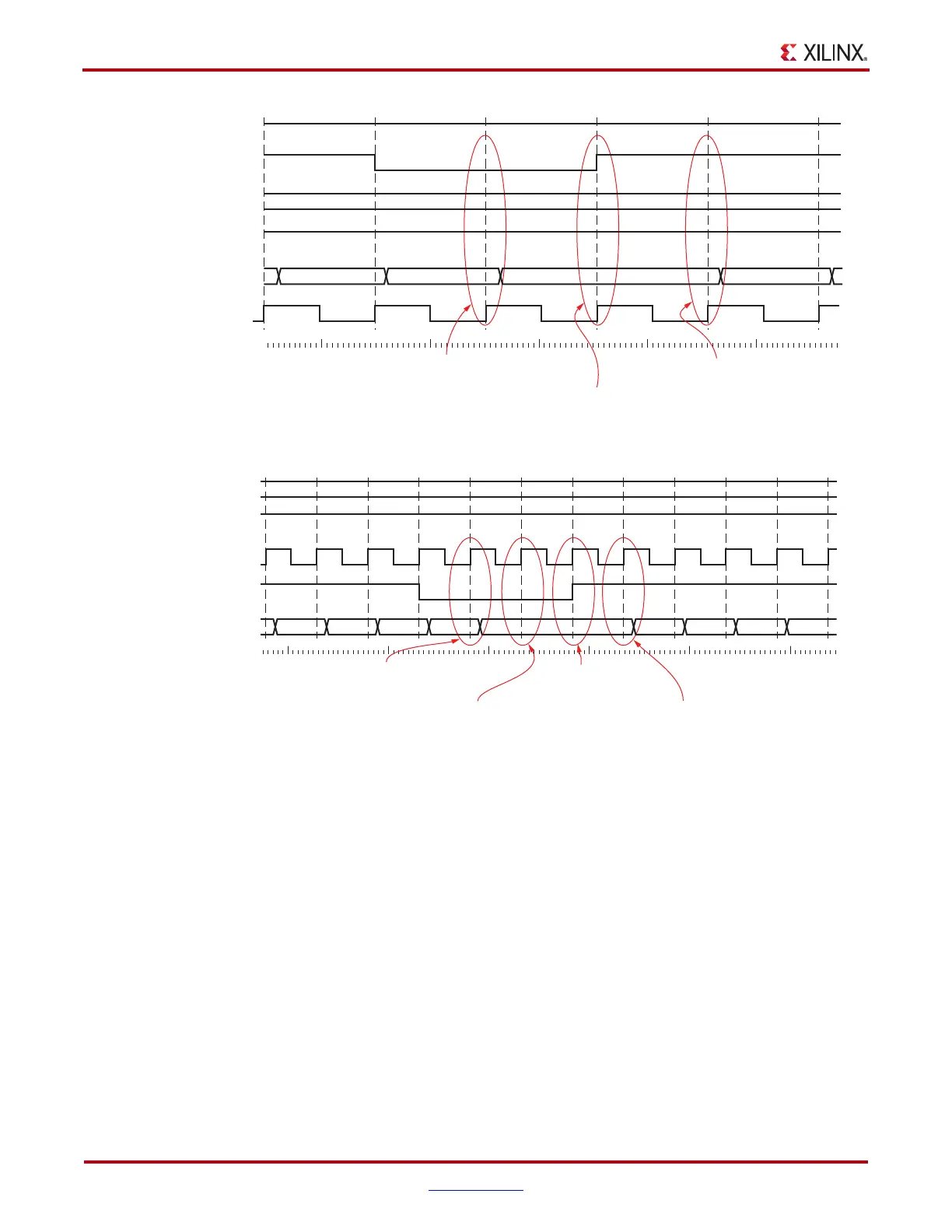

X-Ref Target - Figure 3-19

Figure 3-19: TX Gearbox Internal Sequence Mode, 2-Byte Interface, 64B/66B

UG366_c3_9_051509

1ca6

GEARBOXREADY Low

Data still taken on this cycle.

GEARBOXREADY Low

Data not latched by Gearbox.

GEARBOXREADY Low

Data not latched by Gearbox.

GEARBOXREADY High

Data latched by Gearbox.

919a 4a95 2e71 58c3 1298 dac0 406e 036b

TXHEADER

TXSTA RT SEQ0

TXUSRCLK20

TXGEARBOXREADY0

TXDATA0

1

Loading...

Loading...