5–24 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Differential I/O Interface & Fast PLLs

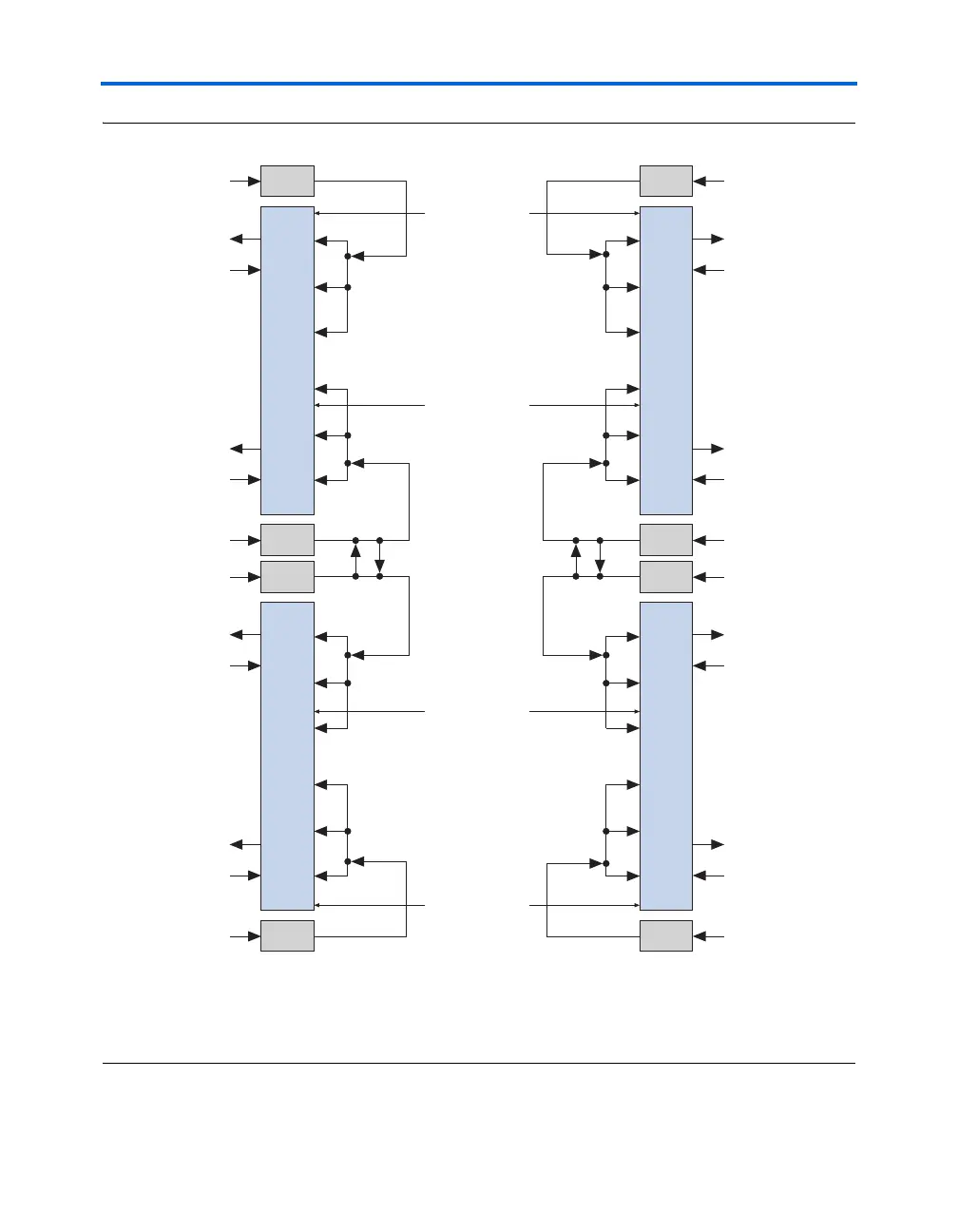

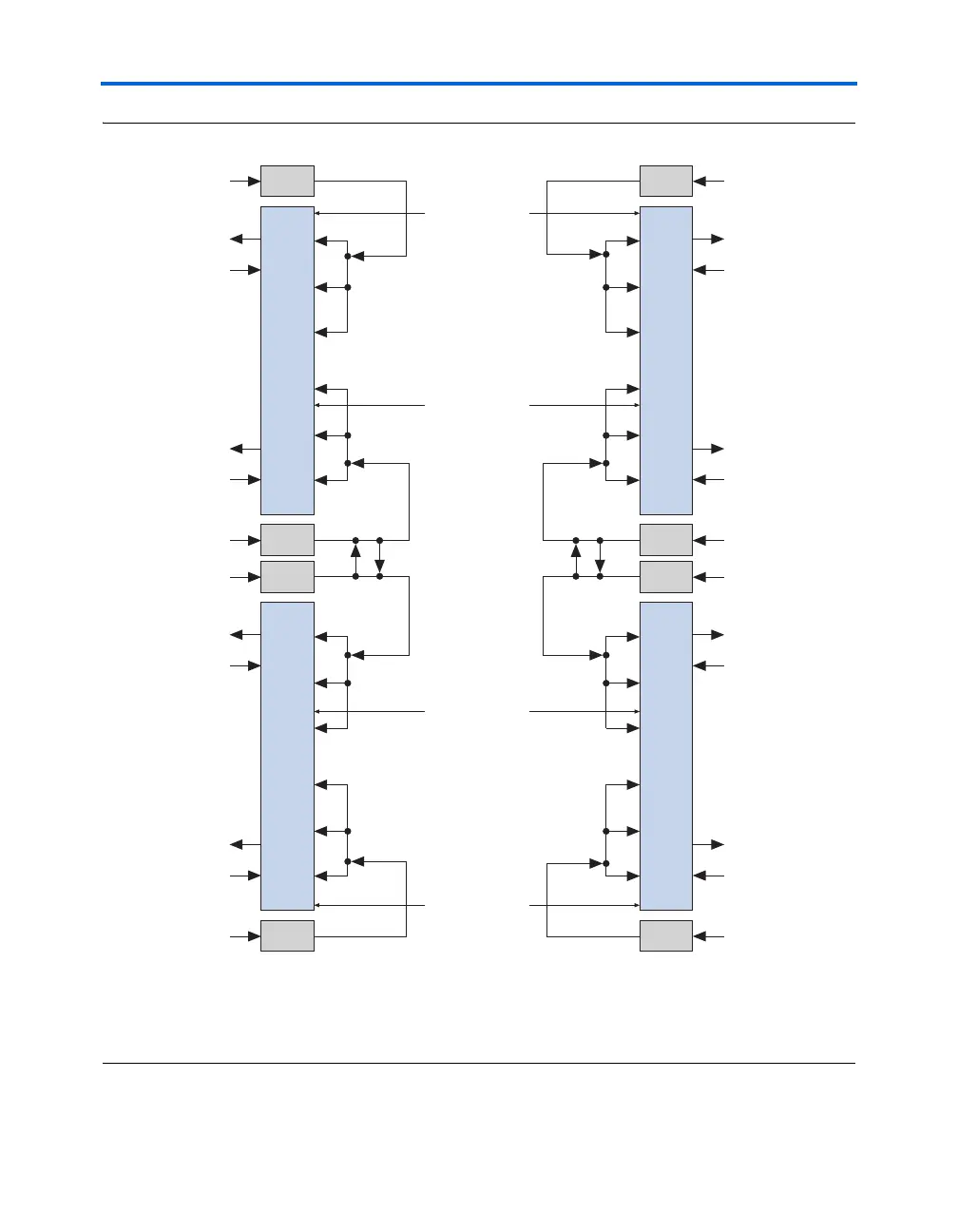

Figure 5–17. Fast PLL & Channel Layout in EP1S30 to EP1S80 Devices Note (1)

Notes to Figure 5–17:

(1) Wire-bond packages only support up to 624-Mbps until characterization shows otherwise.

(2) See Tables 5–10 through 5–14 for the exact number of channels each package and device density supports.

(3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of

its bank quadrant (e.g., if PLL 2 clocks PLL 1’s channel region), those clocked channels support up to 840 Mbps.

Transmitter

Receiver

Transmitter

Receiver

CLKIN

FPLL7CLK

Transmitter

Receiver

Transmitter

Receiver

CLKIN

FPLL10CLK

Transmitter

Receiver

Transmitter

Receiver

FPLL9CLK

CLKIN

Fast

PLL 7

Fast

PLL 1

Up to 20 Receiver and

20 Transmitter

Channels in 20 Rows (2)

Transmitter

Receiver

Transmitter

Receiver

FPLL8CLK

CLKIN

Fast

PLL 2

Fast

PLL 8

Up to 20 Receiver and

20 Transmitter

Channels in 20 Rows (2)

Up to 20 Receiver and

20 Transmitter

Channels in 20 Rows (2)

Up to 20 Receiver and

20 Transmitter

Channels in 20 Rows (2)

(3) (3)

Fast

PLL 10

Fast

PLL 4

Fast

PLL 3

Fast

PLL 9

Loading...

Loading...