7–28 Altera Corporation

Stratix Device Handbook, Volume 2 September 2004

Finite Impulse Response (FIR) Filters

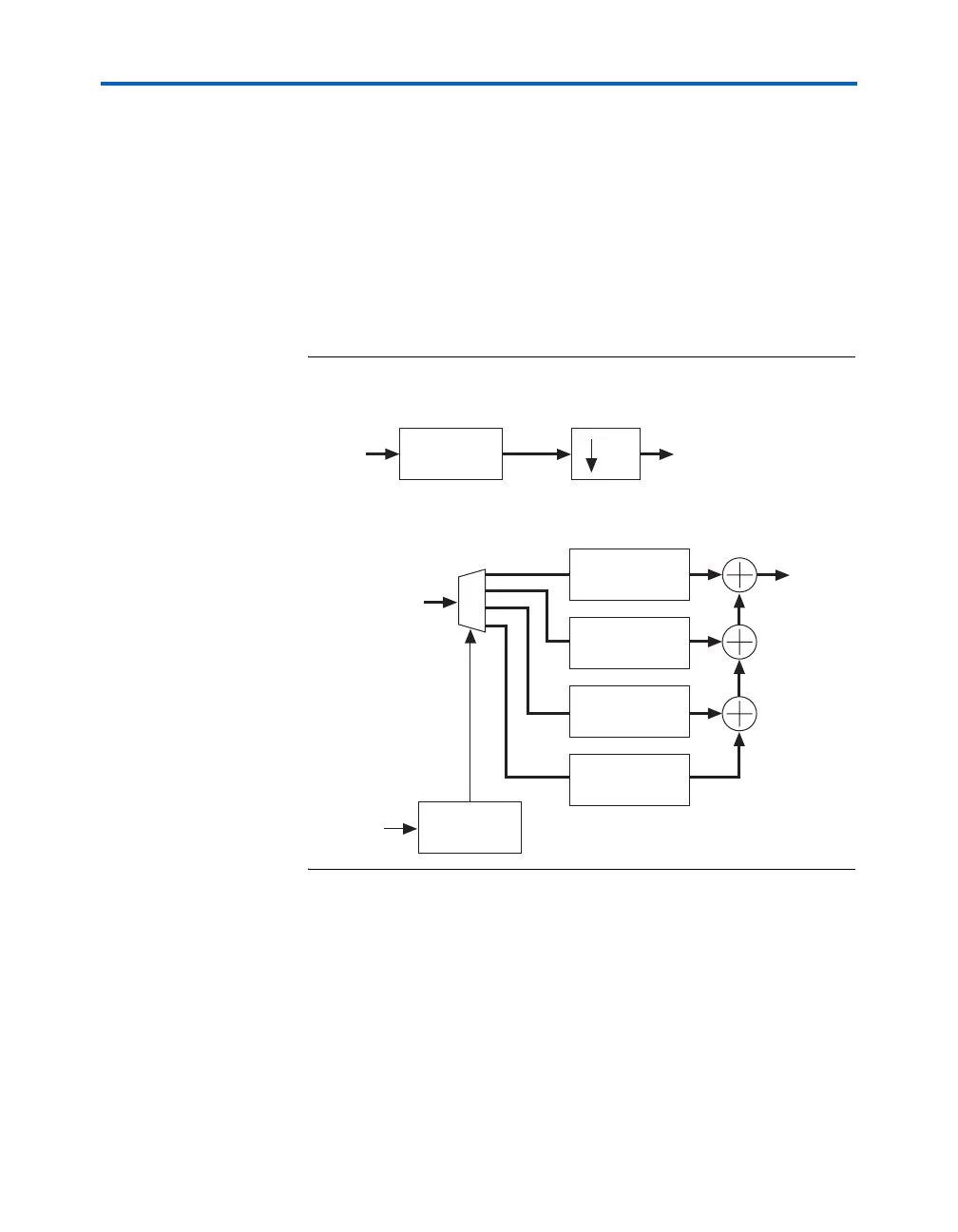

time. The demultiplexer is controlled by a counter, which counts down

modulo-D starting at 0. The overall output is taken by adding the outputs

of all the filters.

The polyphase representation of the decimation filter also reduces the

computational requirement. For the example in Figure 7–16, the direct

implementation requires 16

× D =16× 4 = 64 computations per cycle,

whereas the polyphase implementation requires only 4

× 4 × 1 = 16

computations per cycle. This saving in computational complexity is quite

significant and is often a very convincing reason to use polyphase filters.

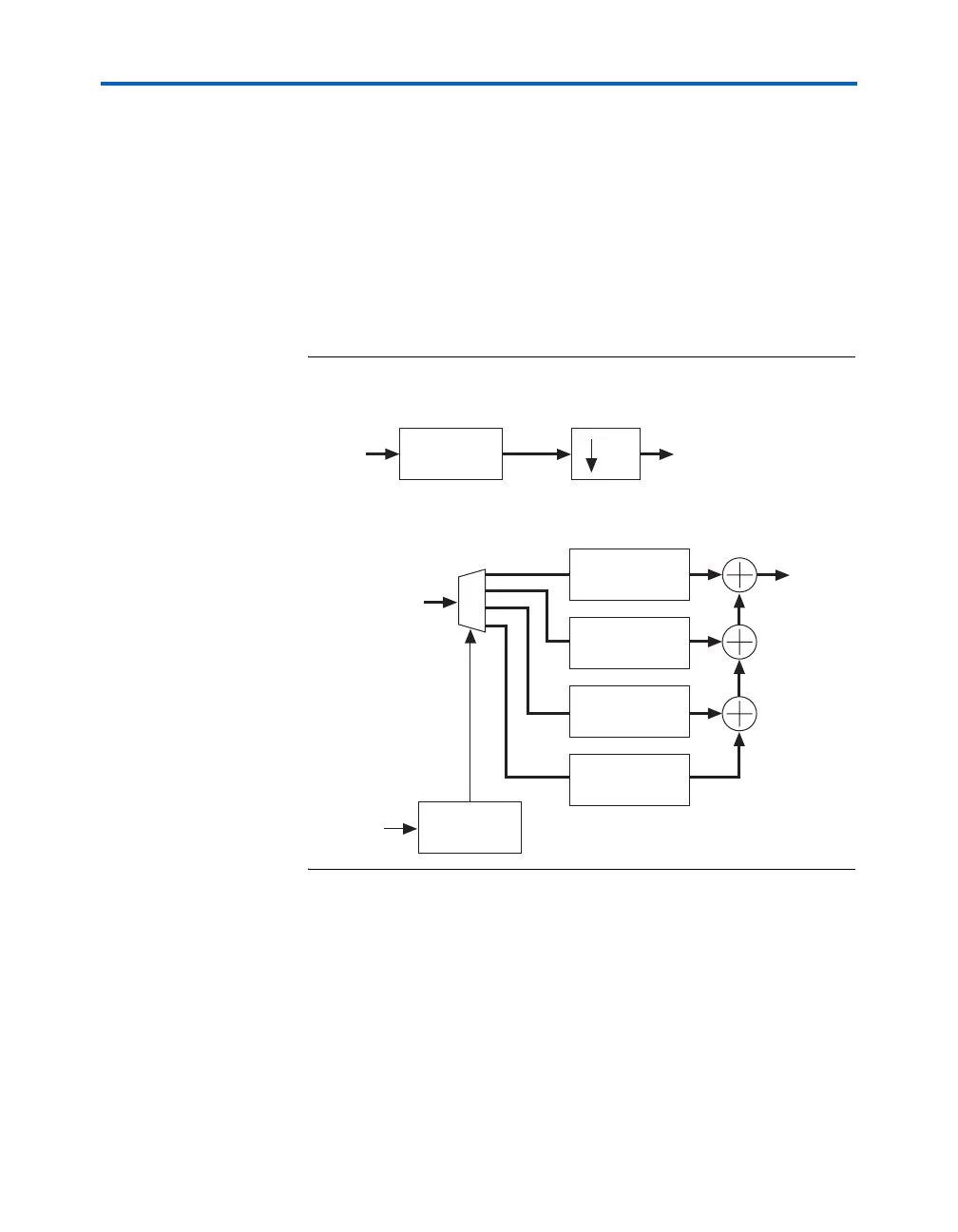

Figure 7–16. Polyphase Filter Representation of a D=4 Decimation Filter

D = 4

LPF with

coefficients

h(0), h(1), ... h(15)

Input

x(n)

Output

y(n)

Decimation Using a Single Low-Pass Filter

Decimation Using a Polyphase Filter

Polyphase filter

with coefficients

h(0), h(4), h(8), h(12)

Polyphase filter

with coefficients

h(1), h(5), h(9), h(13)

Polyphase Filter

with coefficients

h(2), h(6), h(10), h(14)

Polyphase Filter

with coefficients

h(3), h(7), h(11), h(15)

Output

y(n)

Input

x(n)

Modulo 4 down

counter

initialized at 0

4x clock

0

1

2

3

Loading...

Loading...