Altera Corporation 7–29

September 2004 Stratix Device Handbook, Volume 2

Implementing High Performance DSP Functions in Stratix & Stratix GX Devices

Polyphase Decimation Filter Implementation

Figure 7–17 shows the decimation polyphase filter example of

Figure 7–16 as it would fit into Stratix or Stratix GX DSP blocks. The

coefficients of the polyphase filters need to be cycled using the schedule

shown in Table 7–13. The output y(n), is clocked using the 1

× clock.

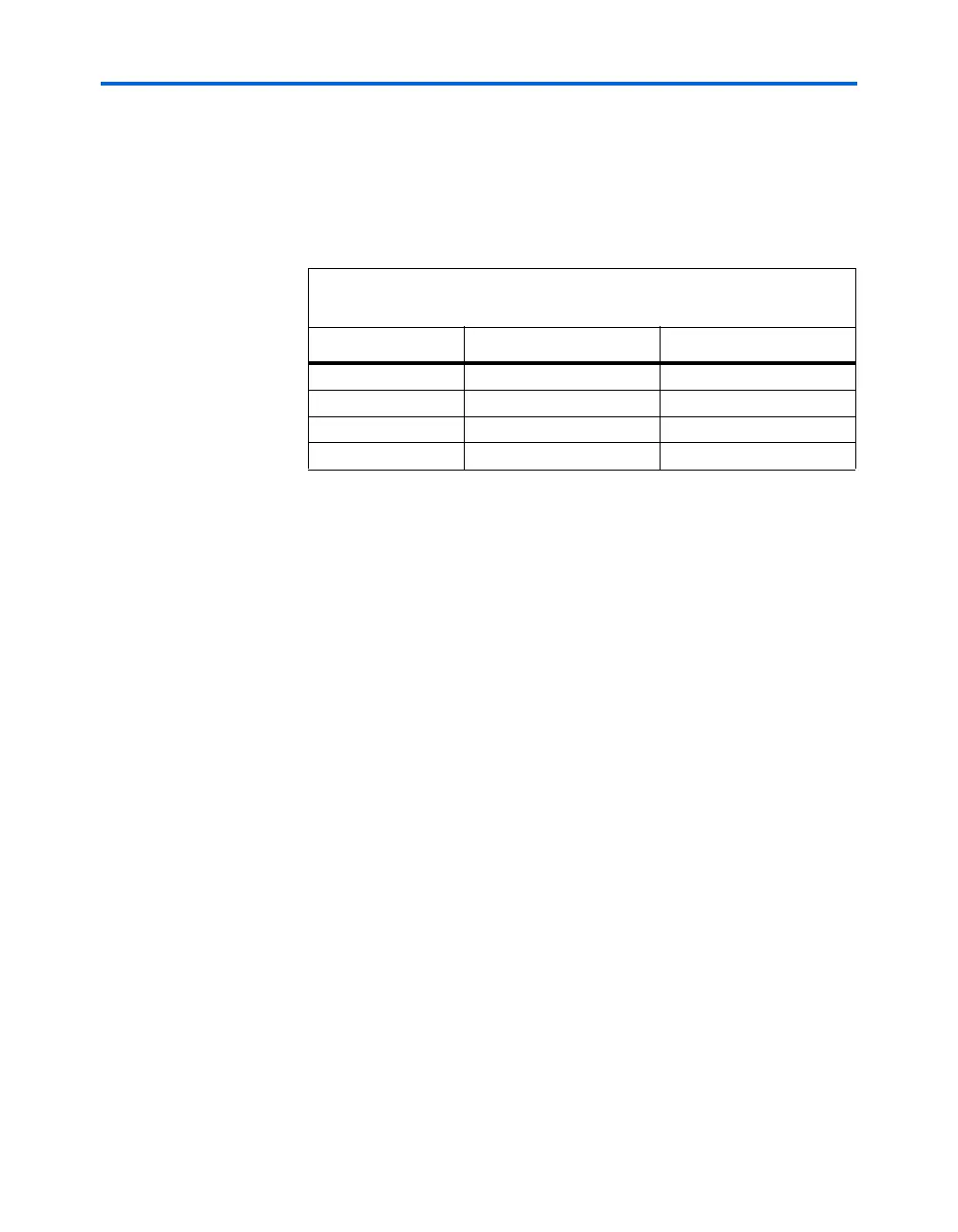

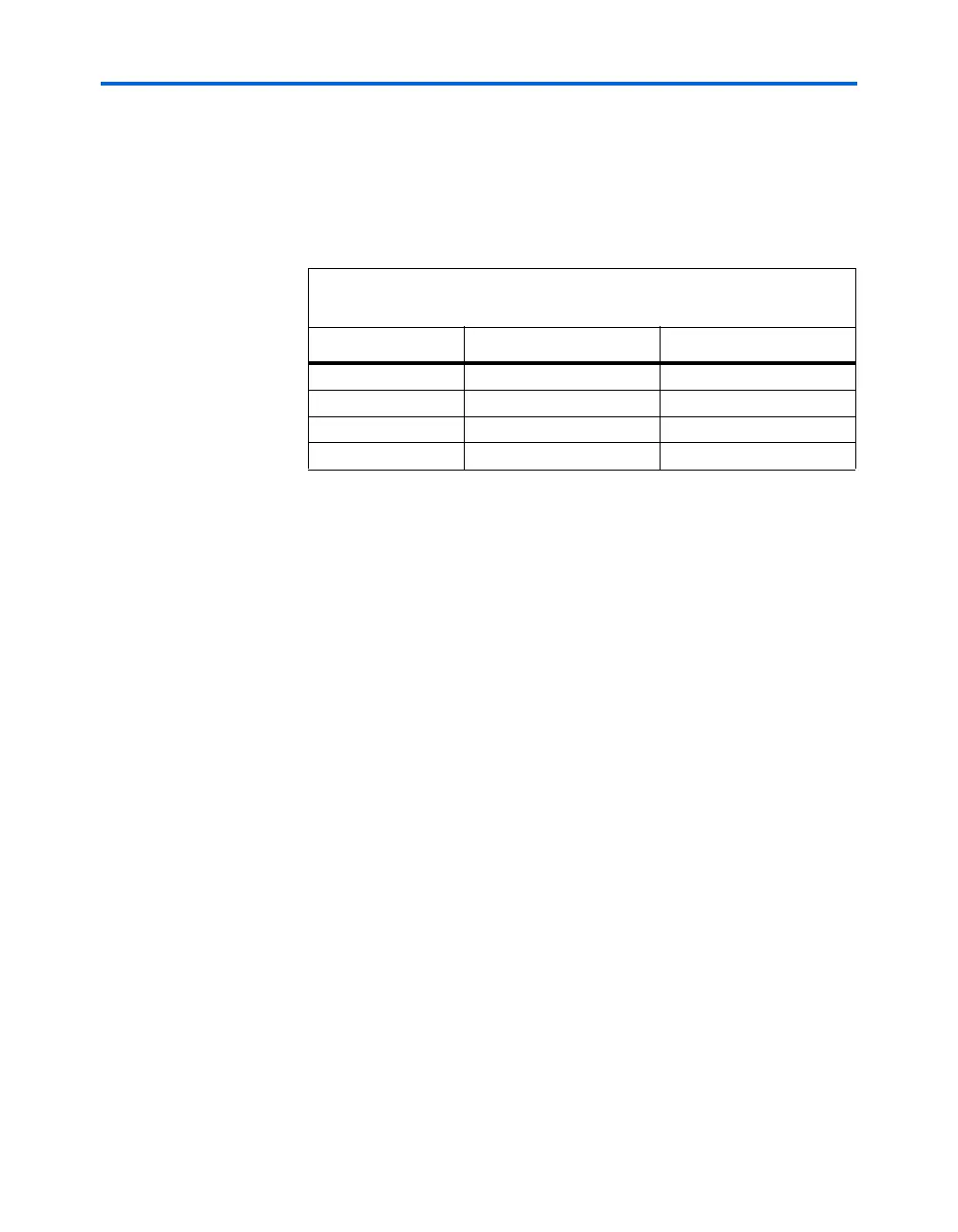

Table 7–13. Coefficient Loading Schedule for Polyphase Decimation Filter

(D=4)

Cycle of 4

× Clock

Coefficients to Load Corresponding RAM/ROM

1, 5,... h(0), h(4), h(8), h(12) 0, 1, 2, 3

2, 6,... h(3), h(7), h(11), h(15) 0, 1, 2, 3

3, 7,... h(2), h(6), h(10), h(14) 0, 1, 2, 3

4, 8,... h(1), h(5), h(9), h(13) 0, 1, 2, 3

Loading...

Loading...