Altera Corporation 7–51

September 2004 Stratix Device Handbook, Volume 2

Implementing High Performance DSP Functions in Stratix & Stratix GX Devices

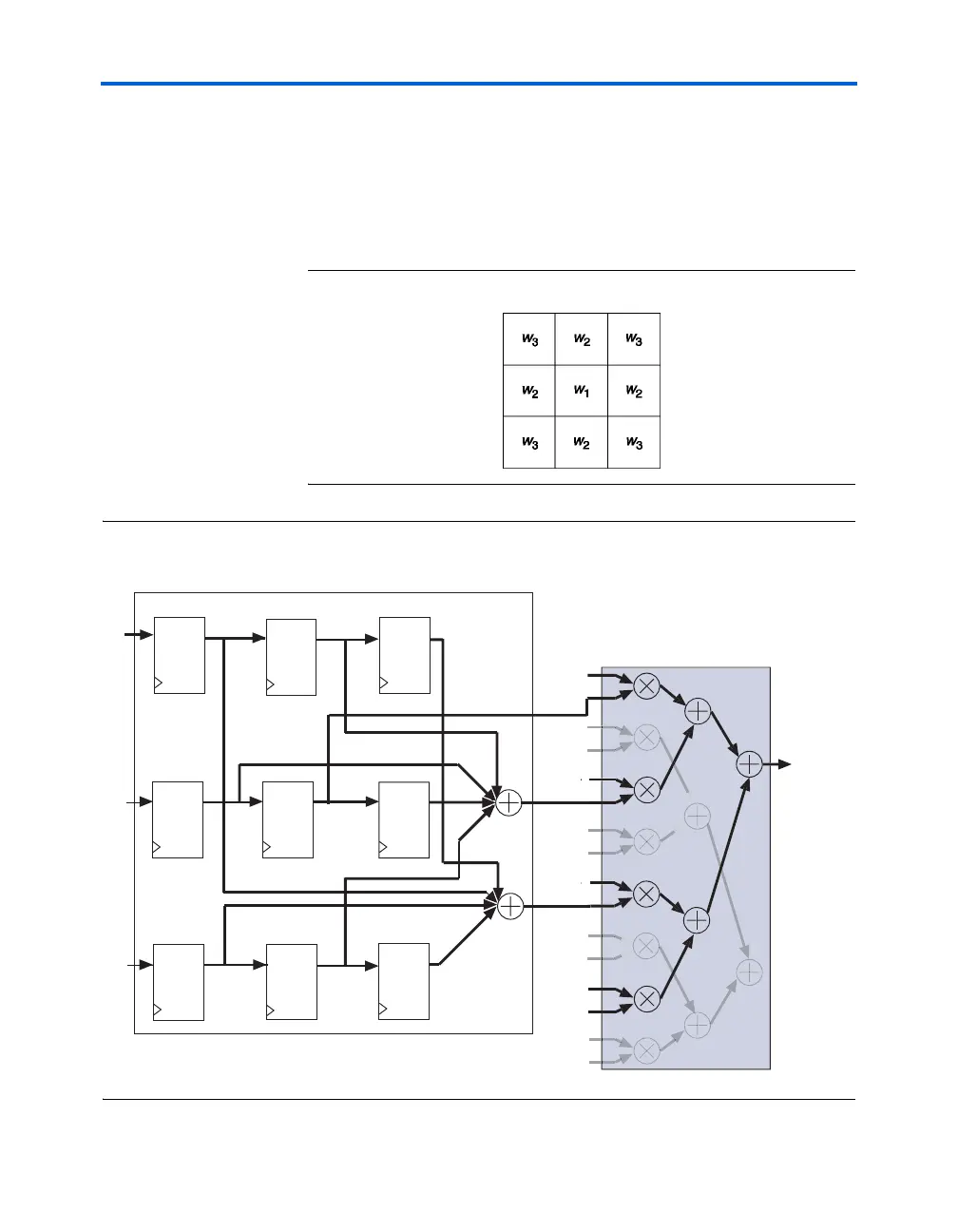

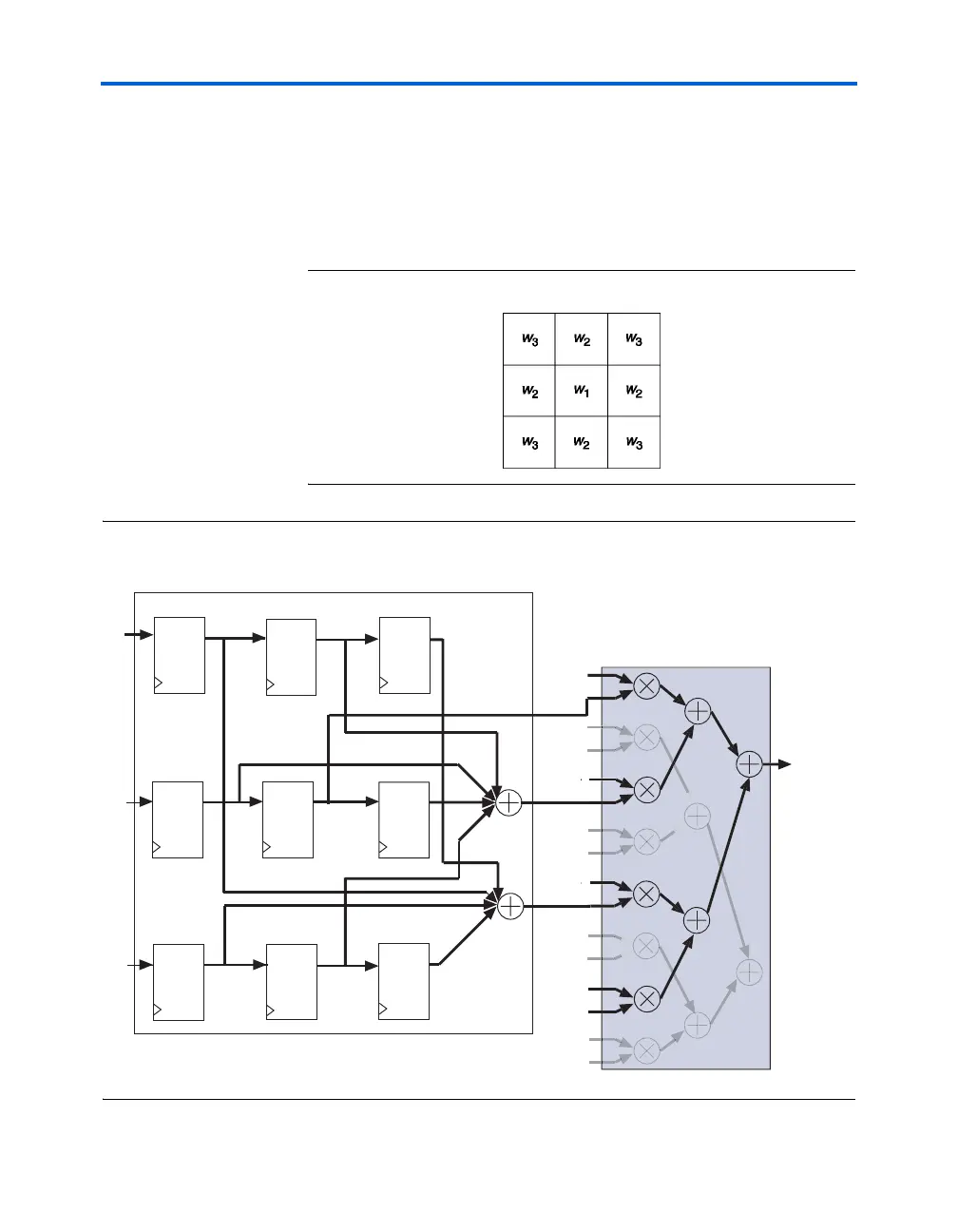

In cases where a symmetric 2-D filter is used, pixels sharing the same

filter coefficients from three separate line-stores A, B, and C can be added

together prior to the multiplication operation. This reduces the number of

multipliers used. Referring to Figure 7–30, w

1

, w

2

, and w

3

are the filter

coefficients. Figure 7–31 shows the implementation of this circular

symmetric filter.

Figure 7–30. Symmetric 3 × 3 Kernel

Figure 7–31. Details on Implementation of Symmetric 3 × 3 Convolution Filter Block

DSP Block - Four Multipliers

Adder Mode (9-bit)

Logic Elements

N

w

1

(m , n )

N

A

B

C

Note: Unused multipliers and adders grayed out. These

multipliers can be used by other functions.

Loading...

Loading...