Altera Corporation 8–9

July 2005 Stratix Device Handbook, Volume 2

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

Stratix and Stratix GX devices contain up to eight fast PLLs. These PLLs

provide high-speed outputs for high-speed differential I/O support as

well as general- purpose clocking with multiplication and phase shifting.

The fast PLL incorporates this 180° phase shift. The Stratix and Stratix GX

device’s data realignment feature enables you to save more logic

elements (LEs). This feature provides a byte-alignment capability, which

is embedded inside the SERDES. The data realignment circuitry can

correct for bit misalignments by slipping data bits.

f For more information about fast PLLs, see the Stratix Device Family Data

Sheet section of the Stratix Device Handbook, Volume 1 or the Stratix GX

Device Family Data Sheet section of the Stratix GX Device Handbook,

Volume 1.

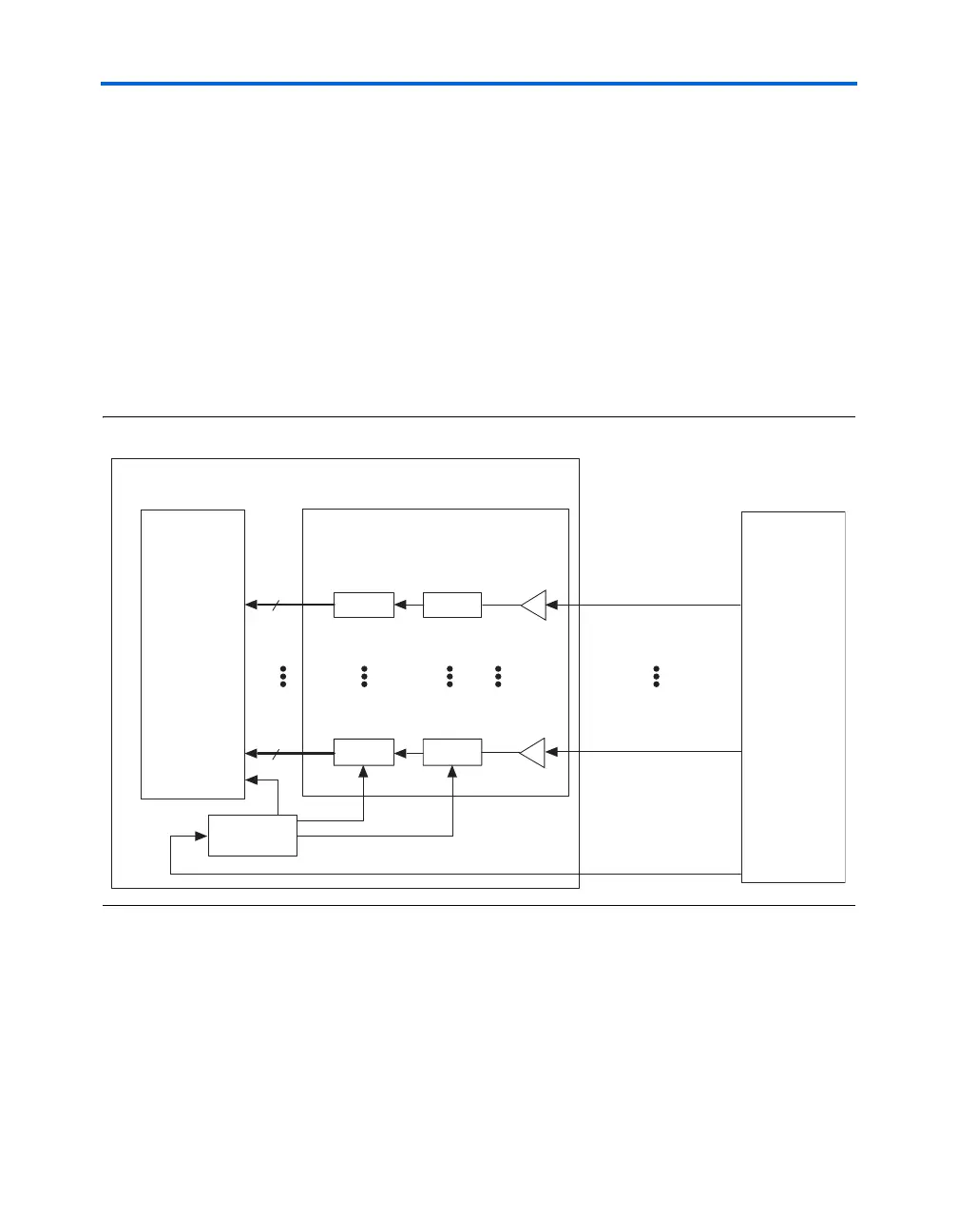

Figure 8–7. Stratix & Stratix GX Device XSBI Receiver Implementation

RX_D[0]

Stratix & Stratix GX

Logic Array

Fast PLL

W = 1

J = 4 or 8

4 or 8

Stratix & Stratix GX SERDES

× W

CH0

CH15

PMA

Receiver

RX_D[15]

PMA_RXCLK_SRC

Stratix & Stratix GX PCS Receiver

÷J

622 MHz

622 MHz

622 Mbps

Parallel

Register

Parallel-to-Serial

Register

4 or 8

Loading...

Loading...