8–8 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Interfaces

The transmit serializer/deserializer (SERDES) clock comes from the

transmitter clock source (PMA_TXCLK_SRC). The receiver SERDES clock

comes from the PMA receiver recovered clock (PMA_RXCLK).

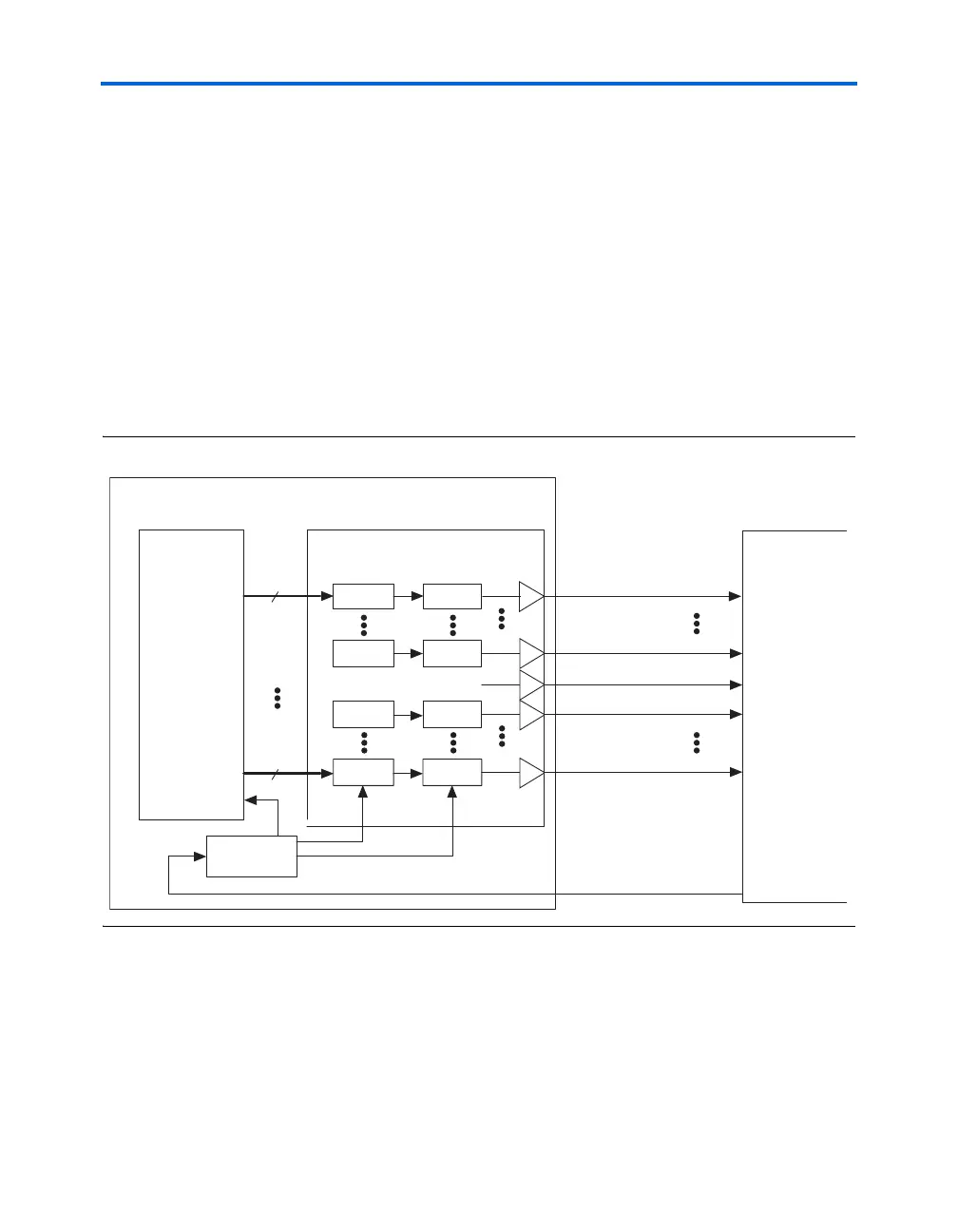

Figure 8–6 shows the transmitter output of the XSBI core. Data

transmitted from the PCS to the PMA starts at the core of the Stratix or

Stratix GX device and travels to the Stratix or Stratix GX transmitter

SERDES block. The transmitter SERDES block converts the parallel data

to serial data for 16 individual channels (TX_D[15..0]). The PMA

source clock (PMA_TXCLK_SRC) is used to clock out the signal data.

PMA_TXCLK is generated from the same phase-locked loop (PLL) as the

data, and it travels to the PMA at the same rate as the data. By using one

of the data channels in the middle of the bus as the clock (in this case, the

eighth channel CH8), the clock-to-data skew improves.

Figure 8–6. Stratix & Stratix GX Device XSBI Transmitter Implementation

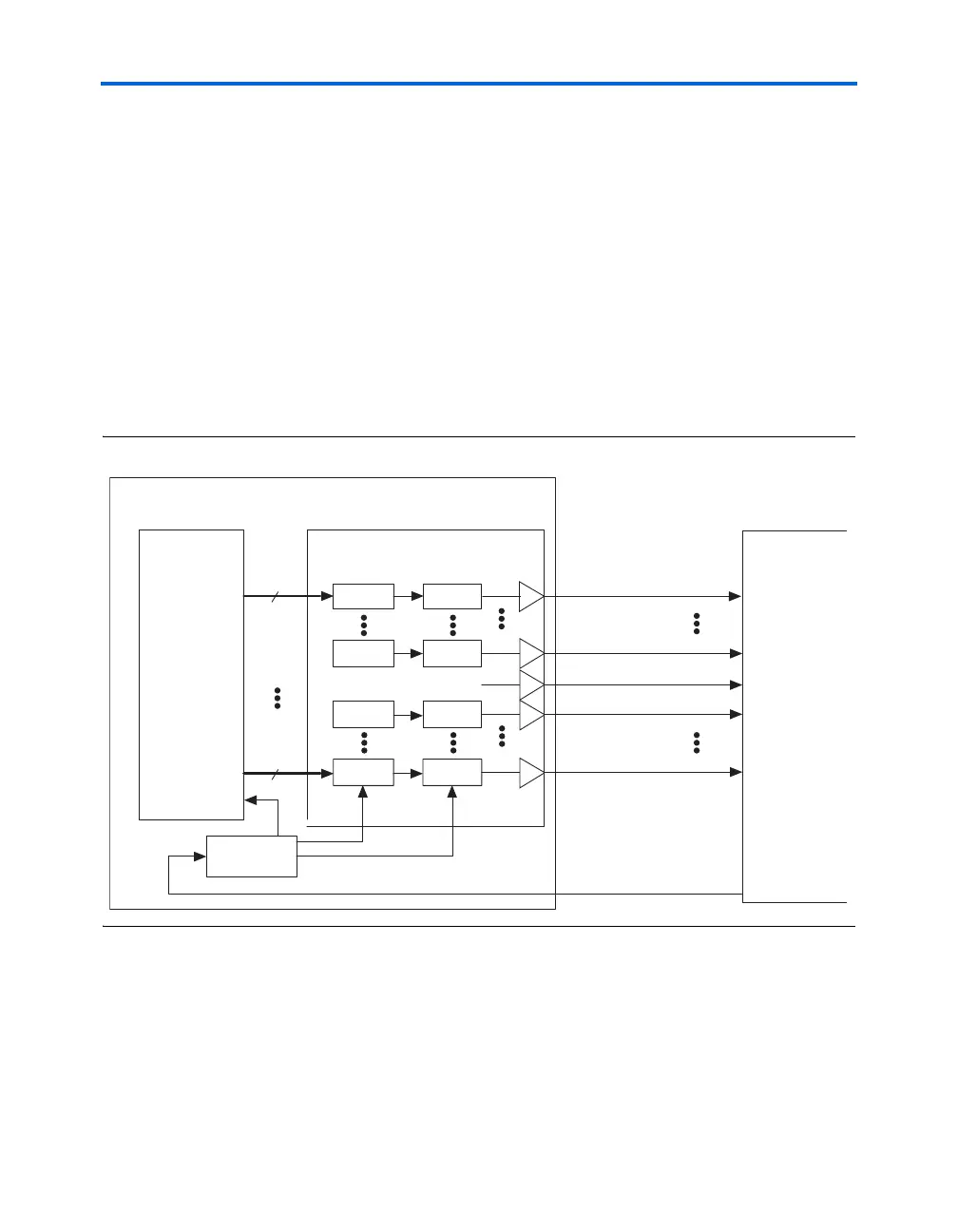

Figure 8–7 shows the receiver input of the XSBI core. From the receiver

side, data (RX_D[15..0]) comes from the PMA to the Stratix or

Stratix GX receiver SERDES block along with the PMA receiver clock

(PMA_RXCLK). The PMA receiver clock is used to convert the serial data

to parallel data. The phase shift or inversion on the PMA receiver clock is

needed to capture the receiver data.

TX_D[0]

Stratix & Stratix GX

Logic Array

Fast PLL

W = 1

J = 4 or 8

4 or 8

Stratix & Stratix GX SERDES

× W

CH0

CH16

PMA

Transmitter

TX_D[15]

PMA_TXCLK_SRC

Stratix & Stratix GX

PCS Transmitter

÷J

622 MHz

622 MHz

622 Mbps

CH9

CH7

Parallel

Register

Parallel-to-Serial

Register

4 or 8

CH8

TX_D[7]

PMA_TXCLK

TX_D[8]

Loading...

Loading...