Altera Corporation 8–7

July 2005 Stratix Device Handbook, Volume 2

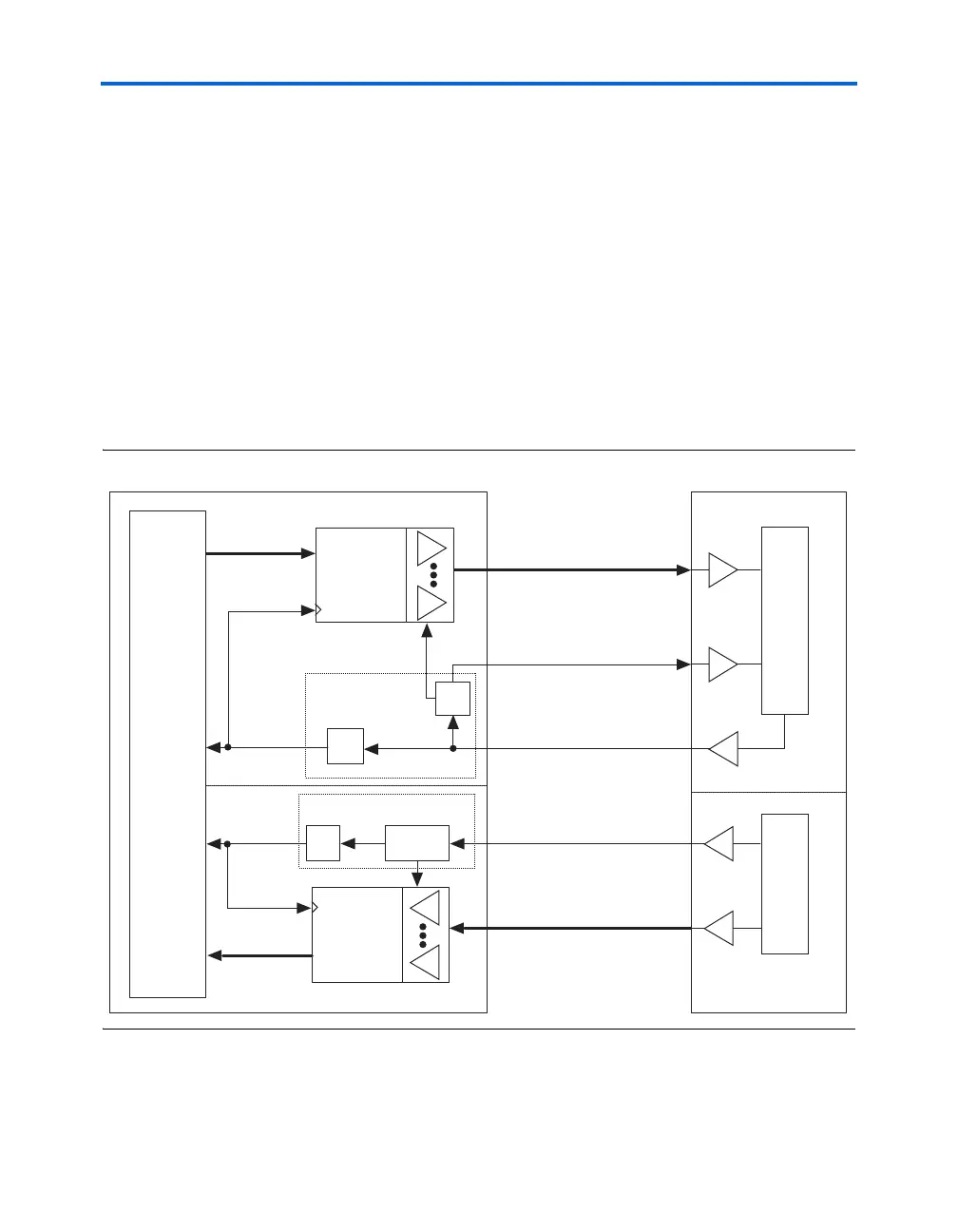

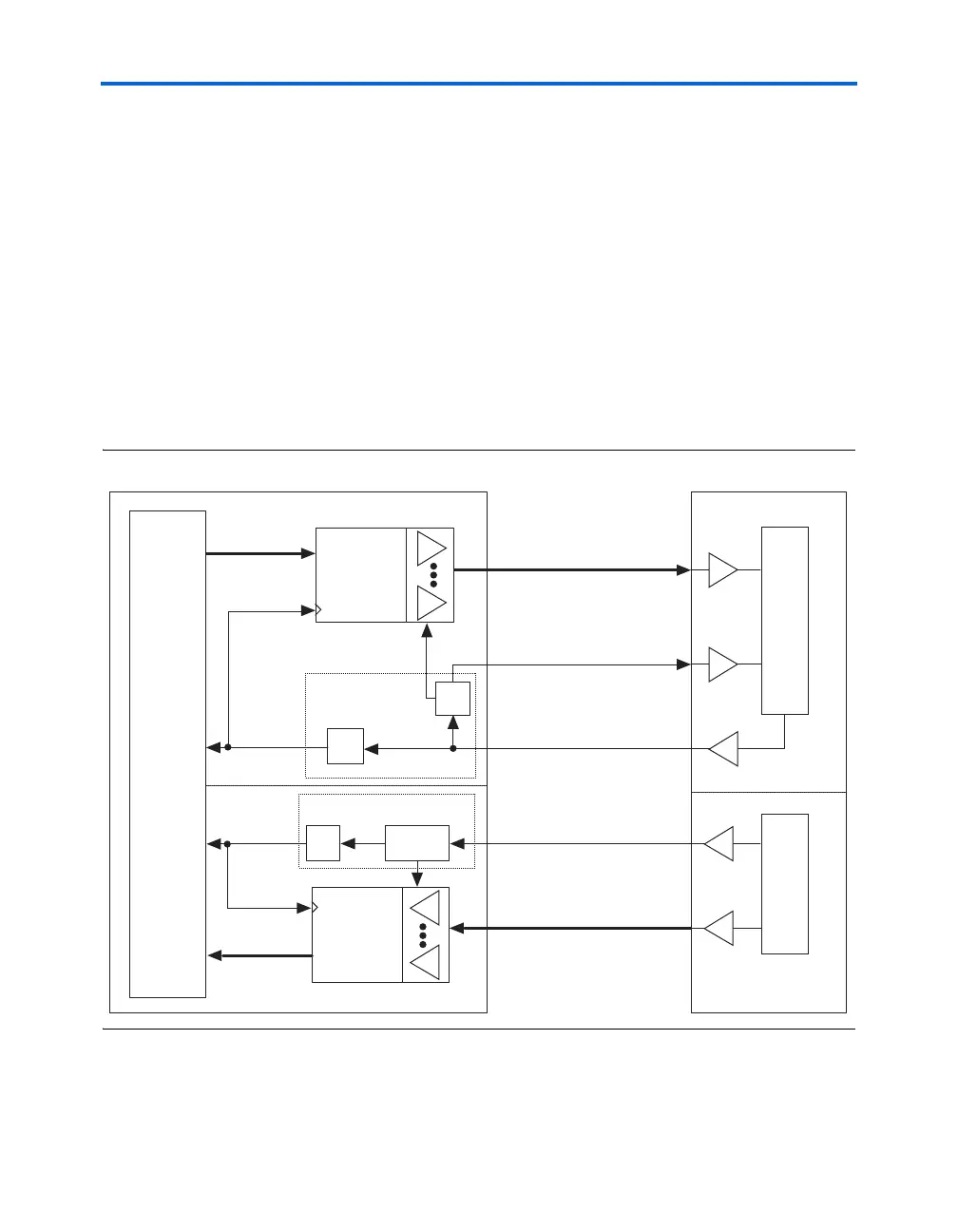

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

Implementation

The 16-bit full duplex LVDS implementation of XSBI in Stratix devices is

shown in Figure 8–5.

The source-synchronous I/O implemented in Stratix GX devices

optionally includes dynamic phase alignment (DPA). DPA automatically

and continuously tracks fluctuations caused by system variations and

self-adjusts to eliminate the phase skew between the multiplied clock and

the serial data, allowing for data rates of 1 Gbps. In non DPA mode the

I/O behaves similarly to that of the Stratix I/O. This document assumes

that DPA is disabled. However, it is simple to implement the same system

with DPA enabled to take advantage of its features. For more information

on DPA, see the Stratix GX Transceivers chapter in the Stratix GX Device

Handbook, Volume 1.

Figure 8–5. Stratix & Stratix GX Device XSBI Implementation

Transmitter

SERDES

Receiver

SERDES

×1

÷8

÷8

180˚

Stratix & Stratix GX PCS

Data

Data

Transmitter

Receiver

PMA

TX_D[15..0]

PMA_TXCLK

PMA_TXCLK_SRC

PMA_RXCLK

RX_D[15..0]

Phase Shift

Receiver

Transmitter

PLL1

PLL2

Stratix &

Stratix GX

Logic Array

Loading...

Loading...