Altera Corporation 8–17

July 2005 Stratix Device Handbook, Volume 2

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

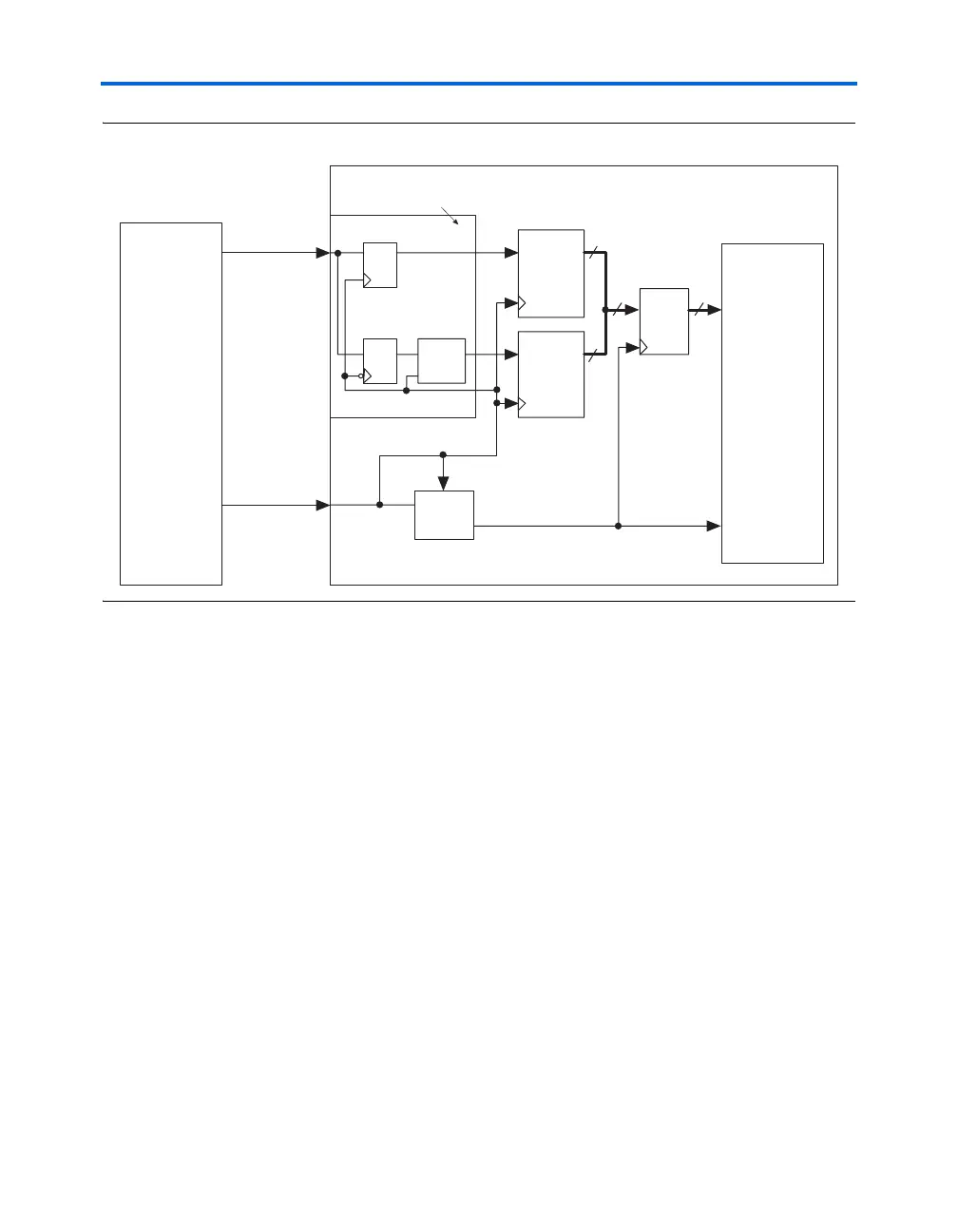

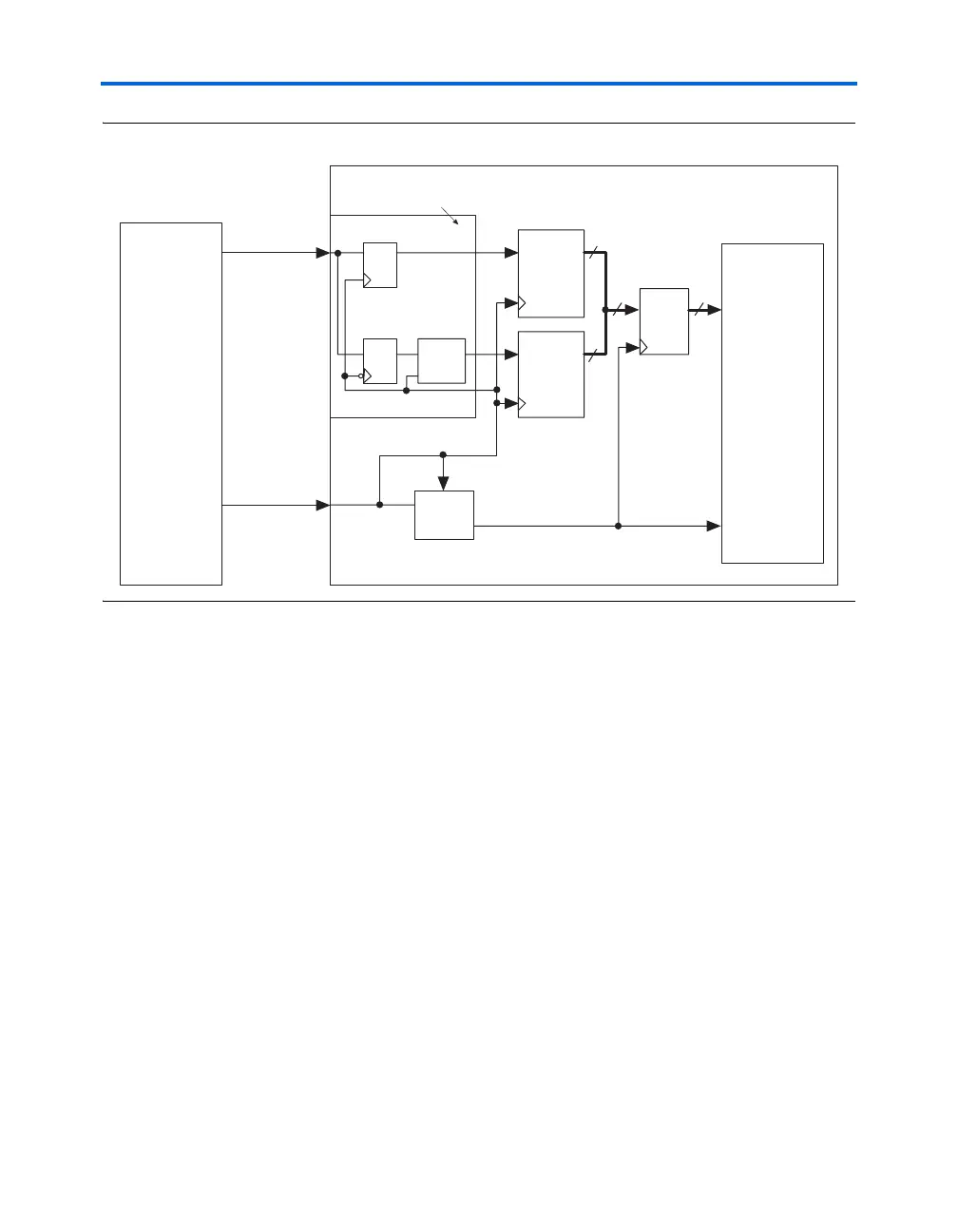

Figure 8–13. Stratix & Stratix GX XGMII Input Implementation (One Channel)

Stratix and Stratix GX devices contain up to four enhanced PLLs. These

PLLs provide features such as clock switchover, spread-spectrum

clocking, programmable bandwidth, phase and delay control, and PLL

reconfiguration. Since the maximum clock rate is 156.25 MHz, you can

use a fast or enhanced PLL for both the XGMII output and input blocks.

f For more information about fast PLLs, see the Stratix Device Family Data

Sheet section of the Stratix Device Handbook, Volume 1 or the Stratix GX

Device Family Data Sheet section of the Stratix GX Device Handbook,

Volume 1.

With this implementation for the XGMII output and input blocks, the

number of XGMII cores per device corresponds to the number of PLLs

each Stratix and Stratix GX device contains. Tables 8–6 and 8–7 show the

number of 1.5-V HSTL I/O pins, PLLs, and XGMII cores that are

supported in each Stratix and Stratix GX device. Each core requires 72 1.5-

TX_D[0]

8 8

MAC_TXCLK

Stratix & Stratix GX PCS Input

156.25 MHz

312.5 Mbps

4

Shift

Register

DDR Input Circuitry

D0,D2,D4,D6

D1,D3,D5,D7

39.0625 MHz

156.25 MHz

MAC

Transmitter

DATA

CLK

Stratix &

DATA

CLK

DFF

DFF Latch

DFF

PLL

4

Shift

Register

÷4

Stratix GX

Logic Array

Loading...

Loading...