Altera Corporation 9–7

July 2005 Stratix Device Handbook, Volume 2

Implementing SFI-4 in Stratix & Stratix GX Devices

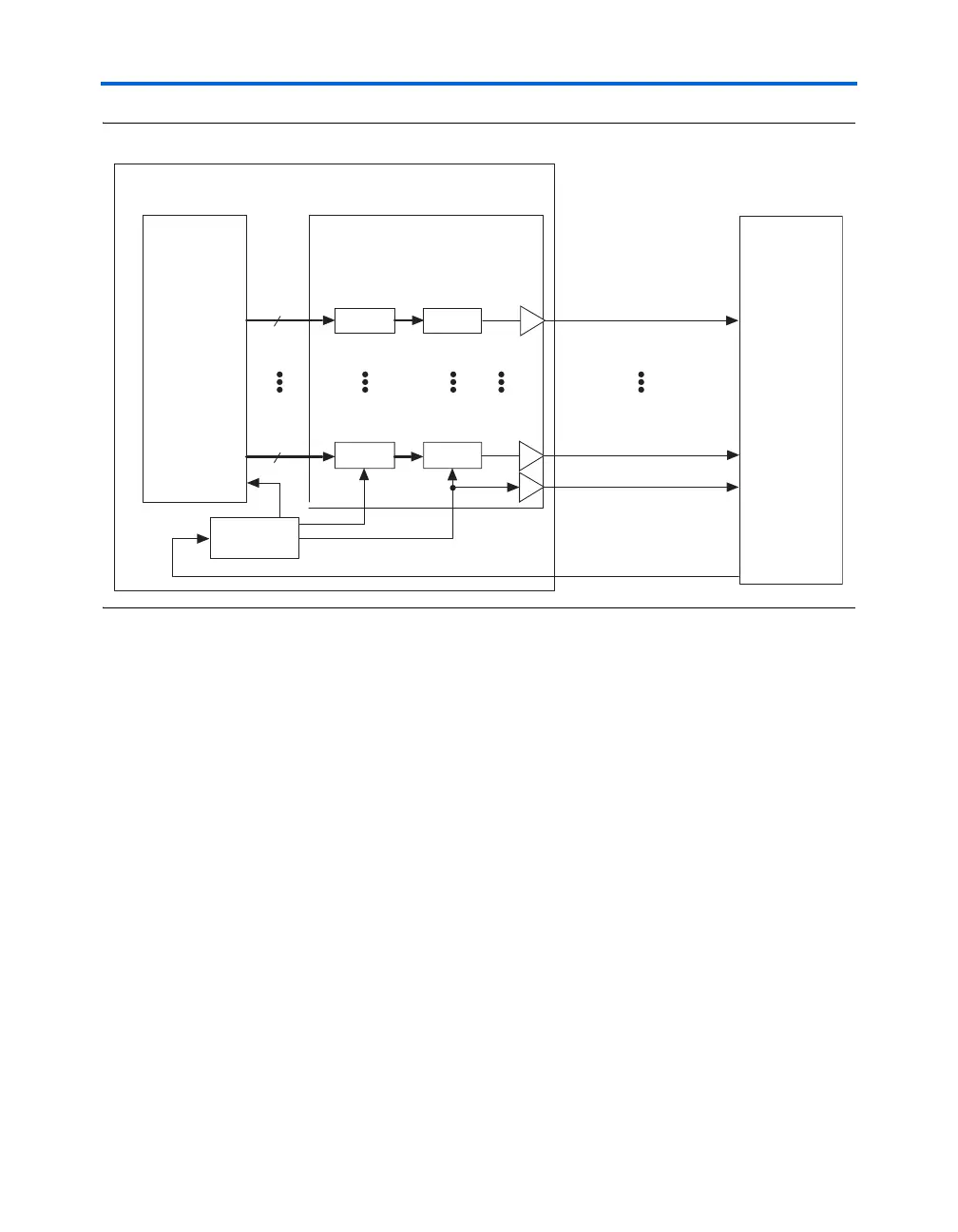

Figure 9–5. Framer Transmitter Interface in Stratix & Stratix GX Devices

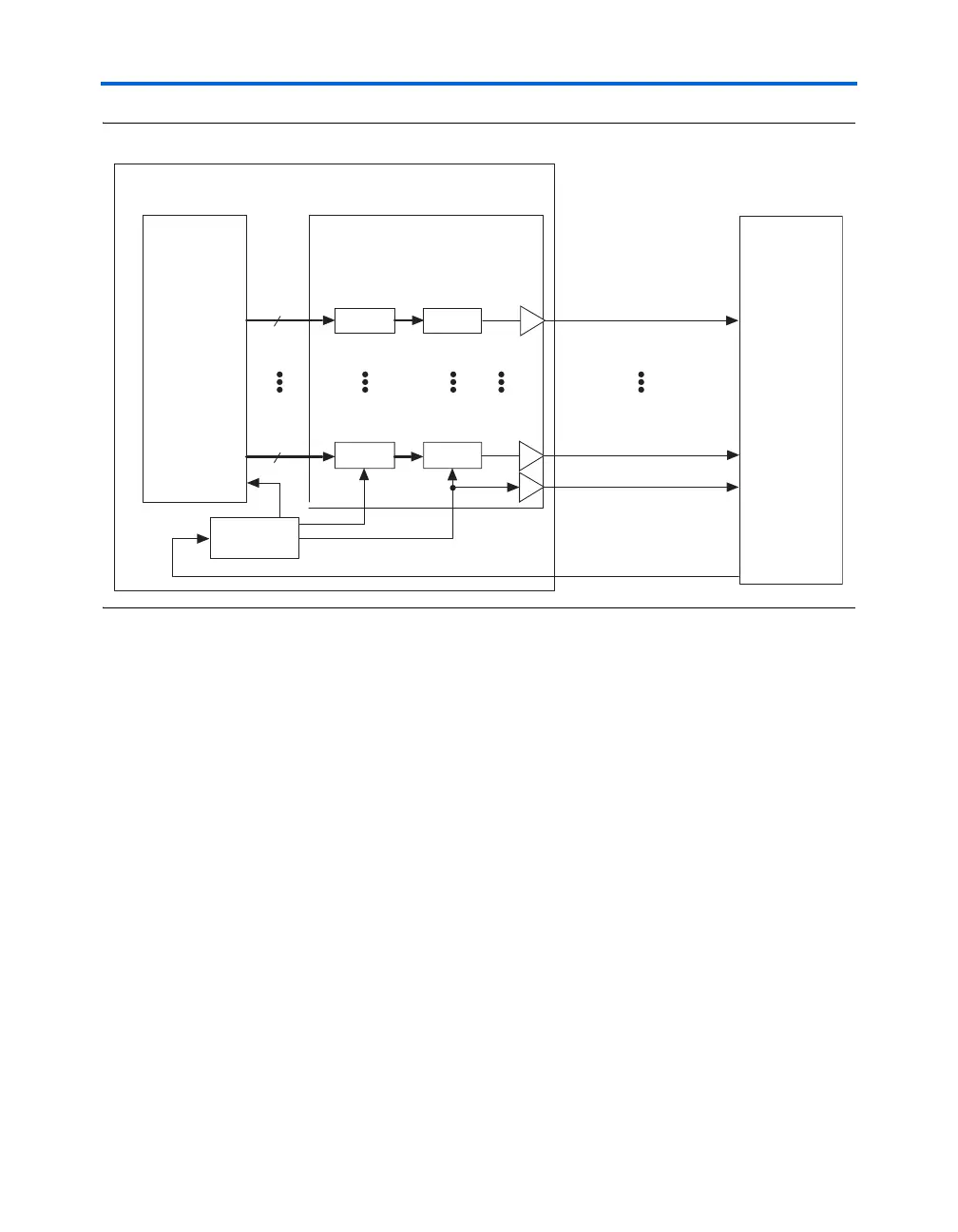

Figure 9–6 shows the receiver block (from Figure 9–4) of the SFI-4 framer

interface implemented in Stratix and Stratix GX devices.

RXDATA[15..0] is received from the OC-192 SERDES on the differential

I/O pins of the Stratix or Stratix GX device. The receiver SERDES

converts the high-speed serial data to parallel. You can generate the

clocks required in the SERDES for parallel and serial data conversion

from the received RXCLK. RXCLK is inverted (phase-shifted by 180°) to

capture received data. While normal I/O operation guarantees that data

is captured, it does not guarantee the parallelization boundary, which is

randomly determined based on the power up of both communicating

devices. The SERDES has embedded data realignment capability, which

can be used to save logic elements (LEs).

TXDATA[0]

Fast PLL

W = 1

J = 8

8

8

Stratix & Stratix GX SERDES

× W

CH0

CH15

OC-192

SERDES

TXDATA[15]

TXCLK

TXCLK_SRC

Stratix & Stratix GX SFI-4 Transmitter

÷J

622 MHz

622 MHz

622MHz

622 Mbps

Parallel

Register

Parallel-to-Serial

Register

Stratix & Stratix GX

Logic Array

Loading...

Loading...