Altera Corporation 10–7

July 2005 Stratix Device Handbook, Volume 2

Transitioning APEX Designs to Stratix & Stratix GX Devices

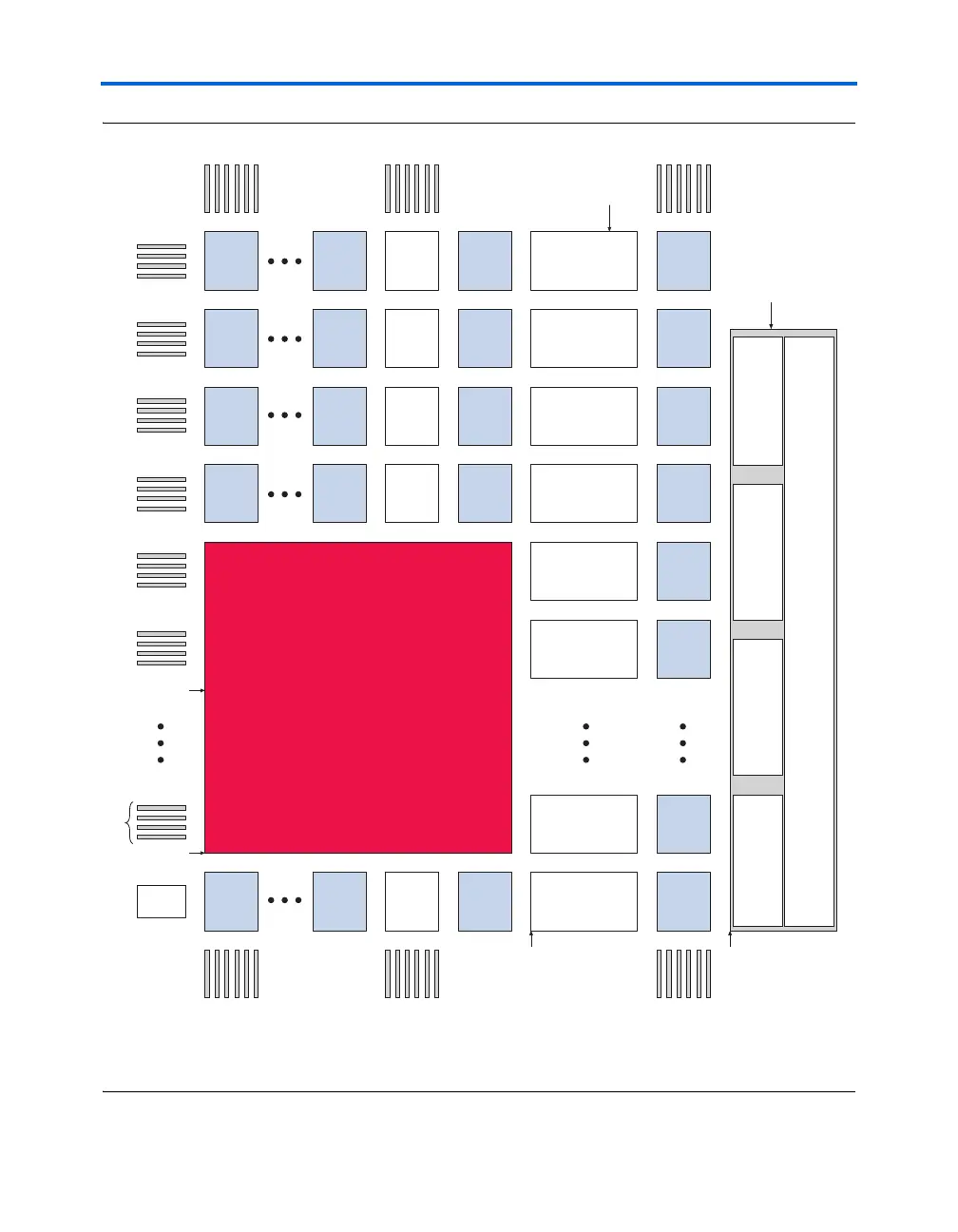

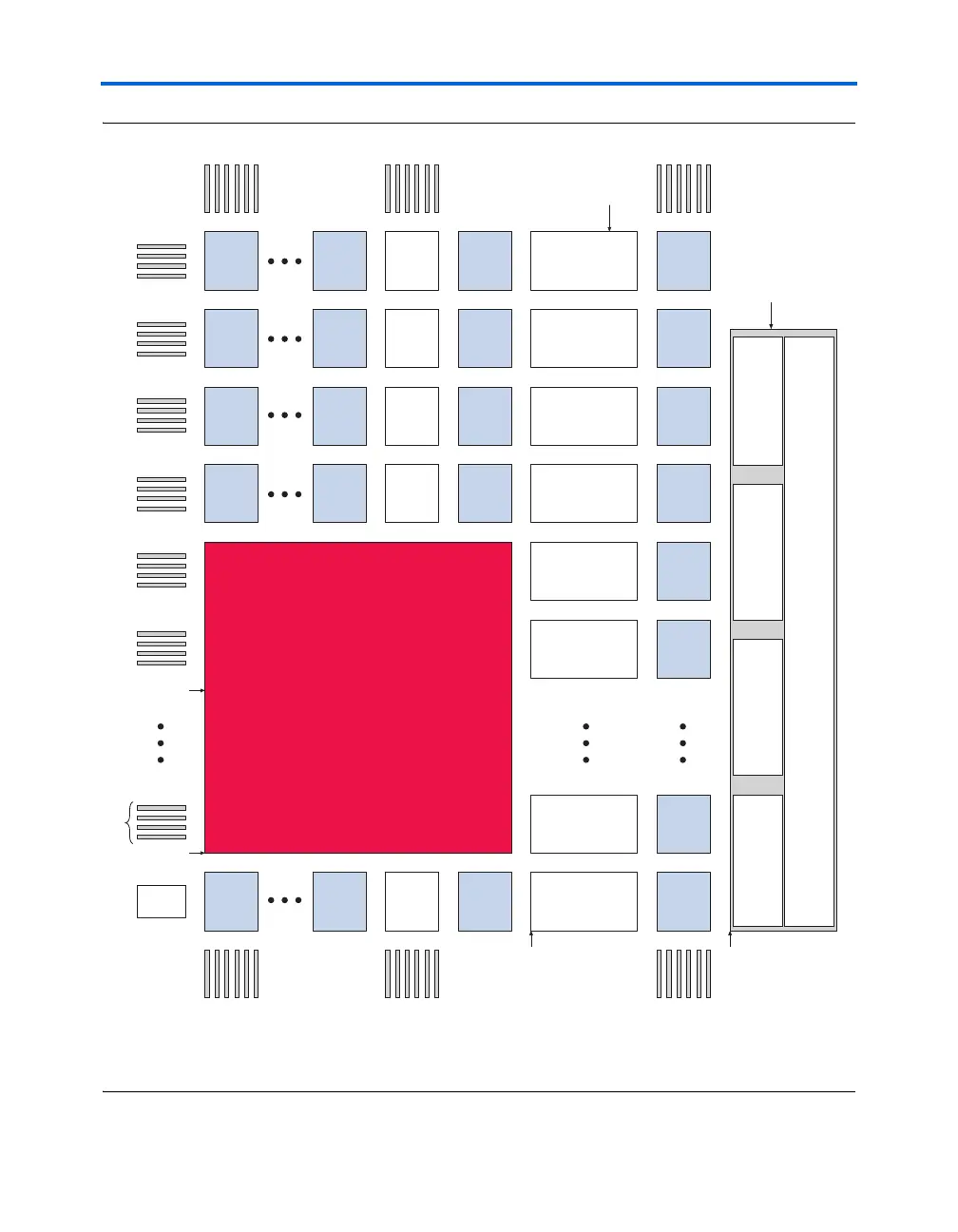

Figure 10–2. Stratix & Stratix GX Architectural Elements Note (1)

Notes to Figure 10–2:

(1) Figure 10–2 shows part of a Stratix and Stratix GX device.

(2) Large block elements use their lower-left corner for the coordinate location.

(3) The Stratix GX architectural elements include transceiver blocks on the right side of the device.

Origin (0, 0)

LAB

(16,18)

LAB

(16,17)

LAB

(16,16)

LAB

(16,15)

LAB

(13,18)

LAB

(13,17)

LAB

(13,16)

LAB

(13,15)

LAB

(11,18)

LAB

(11,17)

LAB

(11,16)

LAB

(11,15)

LAB

(1,18)

LAB

(1,17)

LAB

(1,16)

LAB

(1,15)

M512

(12,18)

M512

(12,17)

M512

(12,16)

M512

(12,15)

LAB

(13,1)

LAB

(11,1)

LAB

(1,1)

PLL

(0,1,0)

M512

(12,1)

LAB

(16,14)

LAB

(16,13)

LAB

(16,2)

LAB

(16,1)

M4K

(14,18)

M4K

(14,17)

M4K

(14,16)

M4K

(14,15)

M4K

(14,14)

M4K

(14,13)

M4K

(14,2)

M4K

(14,1)

M4K RAM Blocks are

Two Units Wide and

One Unit High

Mega RAM (1,2)

DSPMULT

(17,7,0)

and

(17,7,1)

DSPMULT

(17,5,0)

and

(17,5,1)

DSPMULT

(17,3,0)

and

(17,3,1)

DSPMULT

(17,1,0)

and

(17,1,1)

DSPOUT

(18,1,0)

and

(18,1,7)

DSP Block (17,1)

is Two Units Wide

and Eight Units High

(2)

Mega RAM Block is

13 Units Wide and

13 Units High

Pins

(2)(2)

(3

Loading...

Loading...