Altera Corporation 11–59

July 2005 Stratix Device Handbook, Volume 2

Configuring Stratix & Stratix GX Devices

Table 11–16 describes the optional configuration pins. If these optional

configuration pins are not enabled in the Quartus II software, they are

available as general-purpose user I/O pins. Therefore during

configuration, these pins function as user I/O pins and are tri-stated with

weak pull-ups.

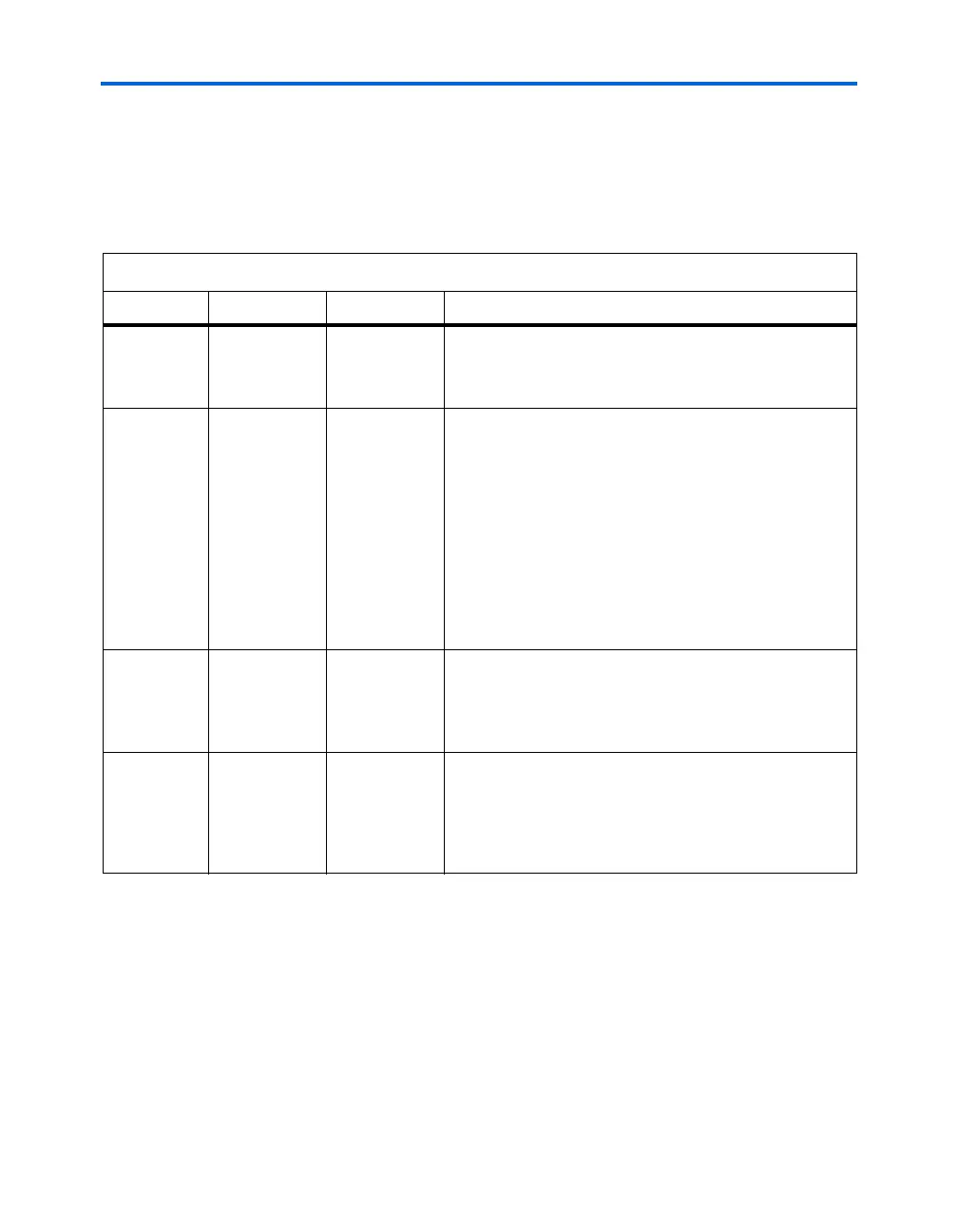

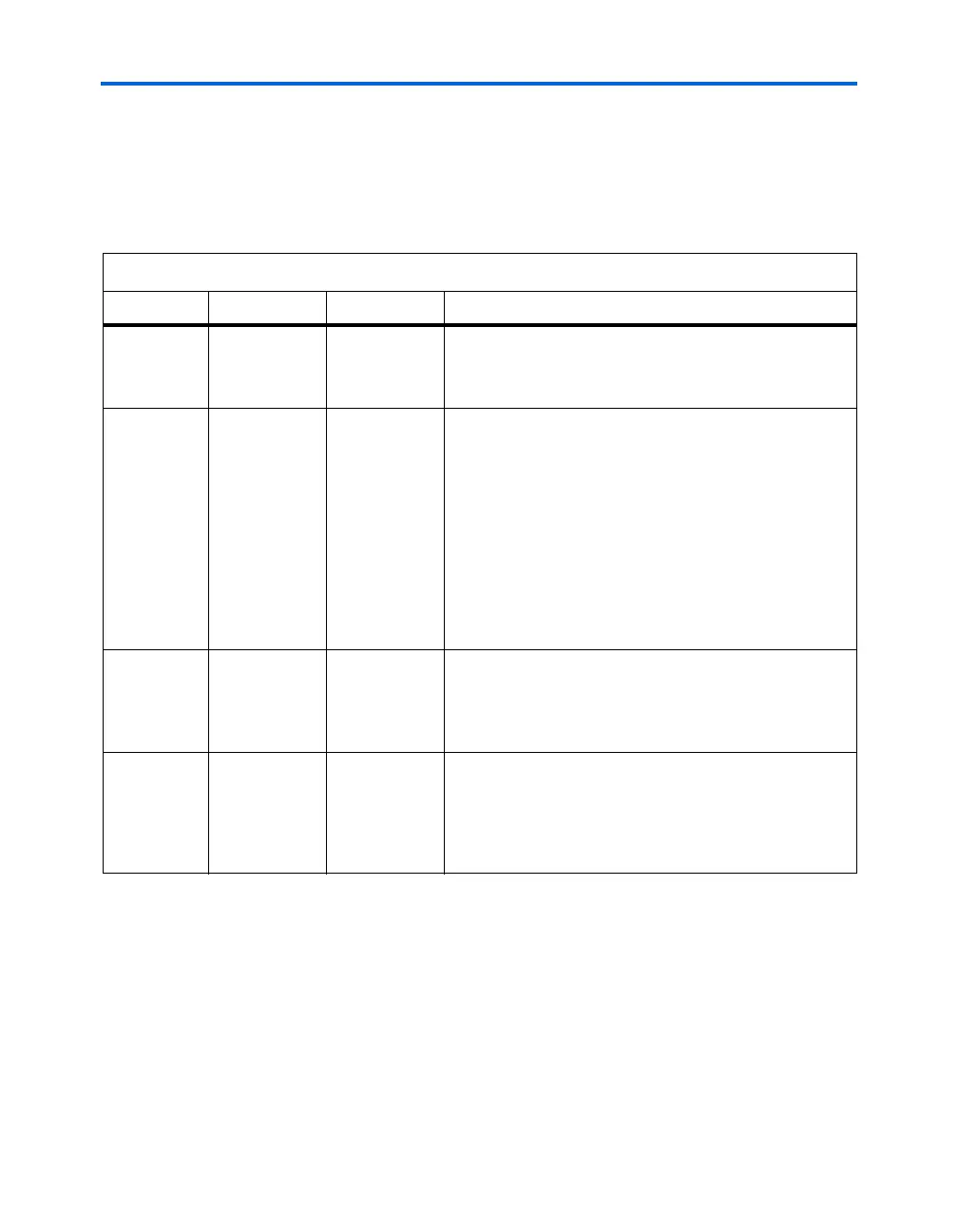

Table 11–16. Optional Configuration Pins

Pin Name User Mode Pin Type Description

CLKUSR

N/A if option is

on. I/O if option

is off.

Input Optional user-supplied clock input. Synchronizes the

initialization of one or more devices. This pin is enabled by

turning on the Enable user-supplied start-up clock

(CLKUSR) option in the Quartus II software.

INIT_DONE

N/A if option is

on. I/O if option

is off.

Output open-

drain

Status pin. Can be used to indicate when the device has

initialized and is in user mode. When

nCONFIG is low and

during the beginning of configuration, the

INIT_DONE pin is

tri-stated and pulled high due to an external 10-kΩ pull-up.

Once the option bit to enable

INIT_DONE is programmed

into the device (during the first frame of configuration data),

the

INIT_DONE pin goes low. When initialization is

complete, the

INIT_DONE pin is released and pulled high

and the FPGA enters user mode. Thus, the monitoring

circuitry must be able to detect a low-to-high transition. This

pin is enabled by turning on the Enable INIT_DONE output

option in the Quartus II software.

DEV_OE

N/A if option is

on. I/O if option

is off.

Input Optional pin that allows the user to override all tri-states on

the device. When this pin is driven low, all I/Os are tri-stated.

When this pin is driven high, all I/Os behave as programmed.

This pin is enabled by turning on the Enable device-wide

output enable (DEV_OE) option in the Quartus II software.

DEV_CLRn

N/A if option is

on. I/O if option

is off.

Input Optional pin that allows you to override all clears on all

device registers. When this pin is driven low, all registers are

cleared. When this pin is driven high, all registers behave as

programmed. This pin is enabled by turning on the Enable

device-wide reset (DEV_CLRn) option in the Quartus II

software.

Loading...

Loading...