1–44 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Clocking

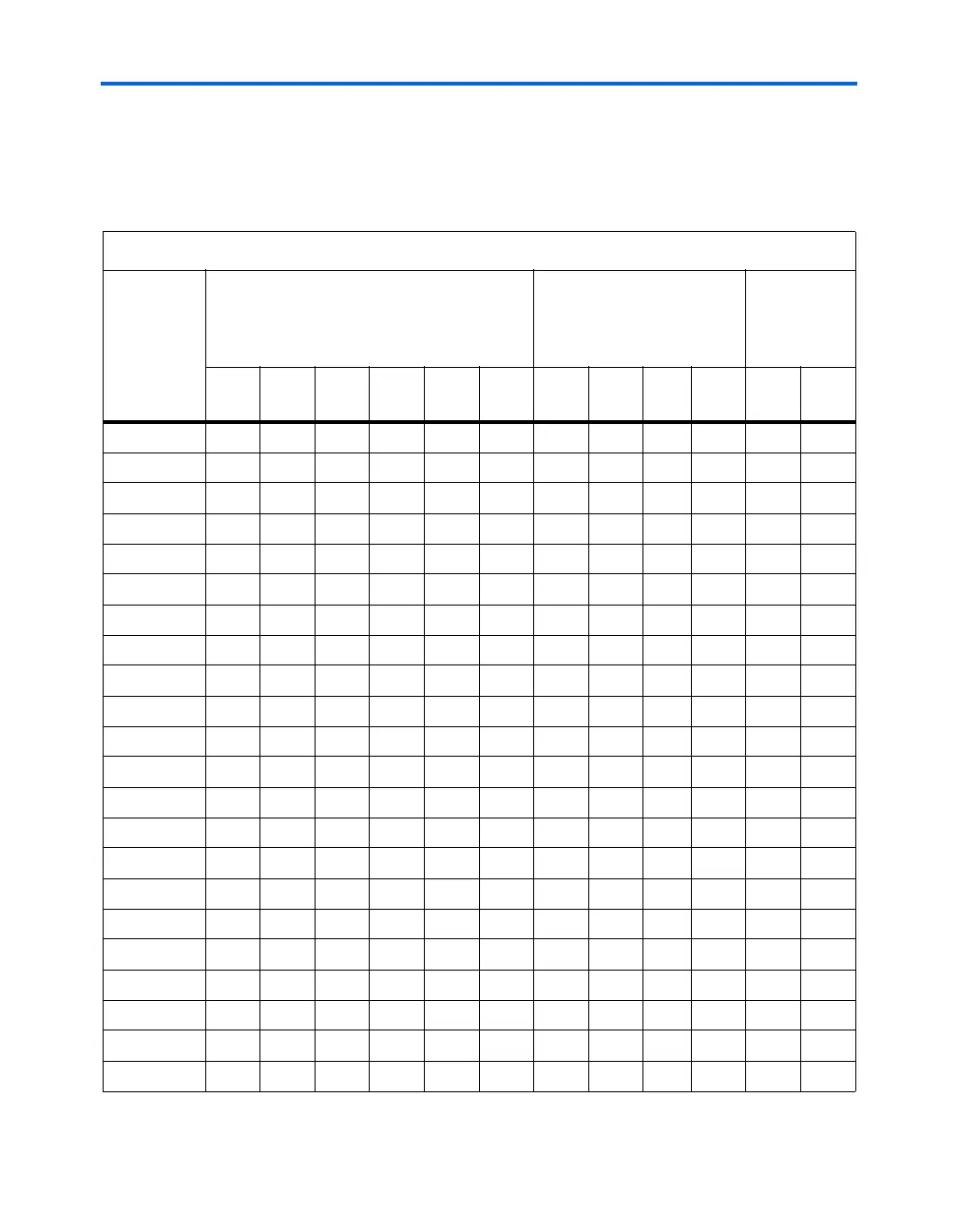

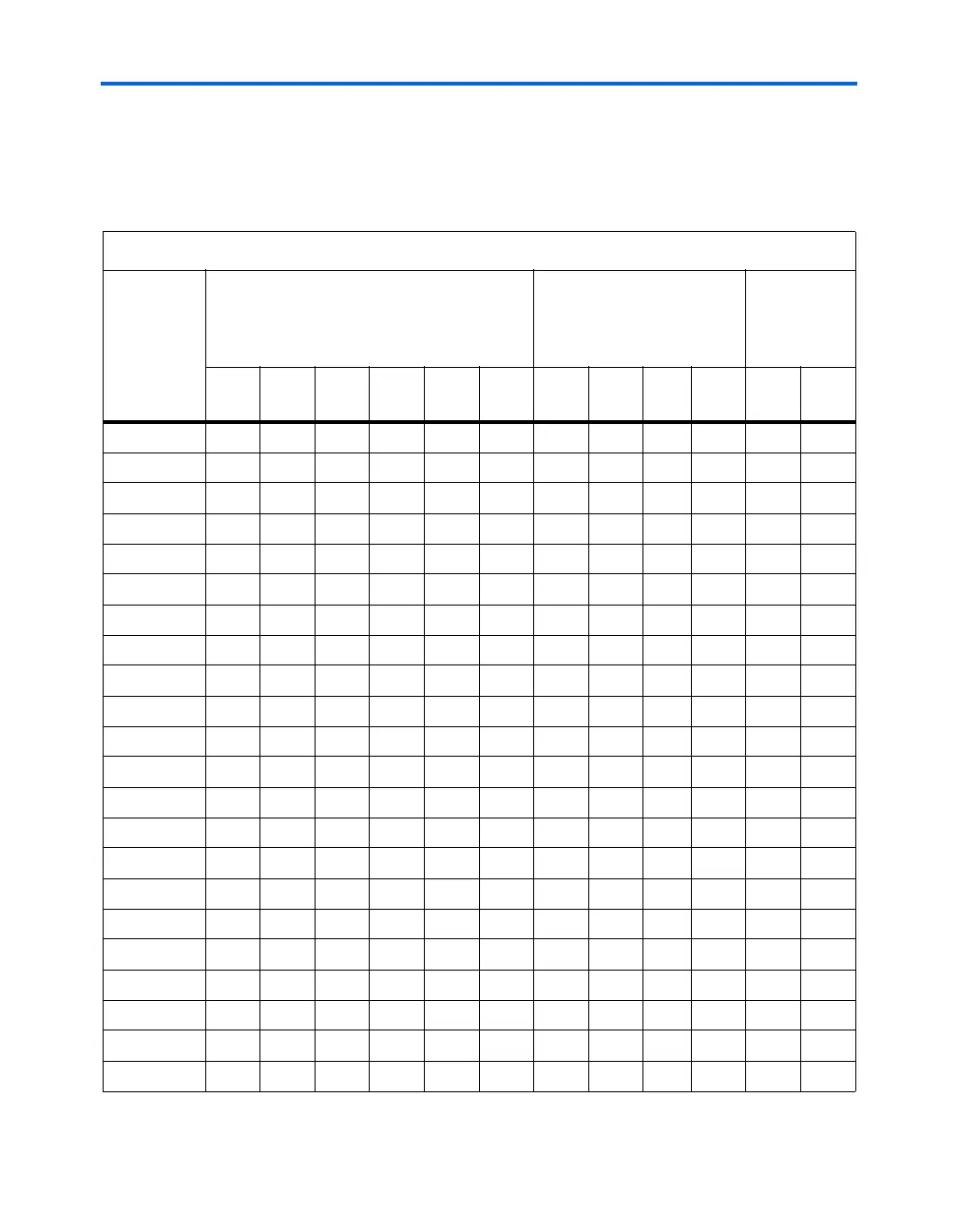

Table 1–15 shows the global and regional clocks that each PLL drives

outputs to for Stratix devices. Table 1–16 shows the global and regional

clock network each of the CLK and

FPLLCLK pins drive when bypassing

the PLL.

Table 1–15. Stratix Global & Regional Clock Output Line Sharing for Enhanced & Fast PLLs (Part 1 of 2)

Clock

Network

All Devices

EP1S30, EP1S40, EP1S60 &

EP1S80 Devices Only

EP1S40 (5),

EP1S60 &

EP1S80

Devices Only

PLL 1

(1)

PLL 2

(1)

PLL 3

(1)

PLL 4

(1)

PLL 5

(2)

PLL 6

(2)

PLL 7

(1)

PLL 8

(1)

PLL

9 (1)

PLL

10 (1)

PLL

11 (2)

PLL

12 (2)

GCLK0

vv vv

GCLK1

vv vv

GCLK2

vv vv

GCLK3

vv vv

GCLK4

vv

GCLK5

vv

GCLK6

vv

GCLK7

vv

GCLK8

vv vv

GCLK9

vv vv

GCLK10

vv vv

GCLK11

vv vv

GCLK12

vv

GCLK13

vv

GCLK14

vv

GCLK15

vv

RCLK0

vv v

RCLK1

vv v

RCLK2

vv

RCLK3

vv

RCLK4

vv v

RCLK5

vv v

Loading...

Loading...