Altera Corporation 2–5

July 2005 Stratix Device Handbook, Volume 2

TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices

M-RAM Blocks

M-RAM blocks support byte enables for the × 16, ×18, × 32, ×36, × 64, and

× 72 modes. In the ×128 or × 144 simple dual-port mode, the two sets of

byteena signals (byteena_a and byteena_b) combine to form the

necessary 16 byte enables. Tables 2–5 and 2–6 summarize the byte

selection.

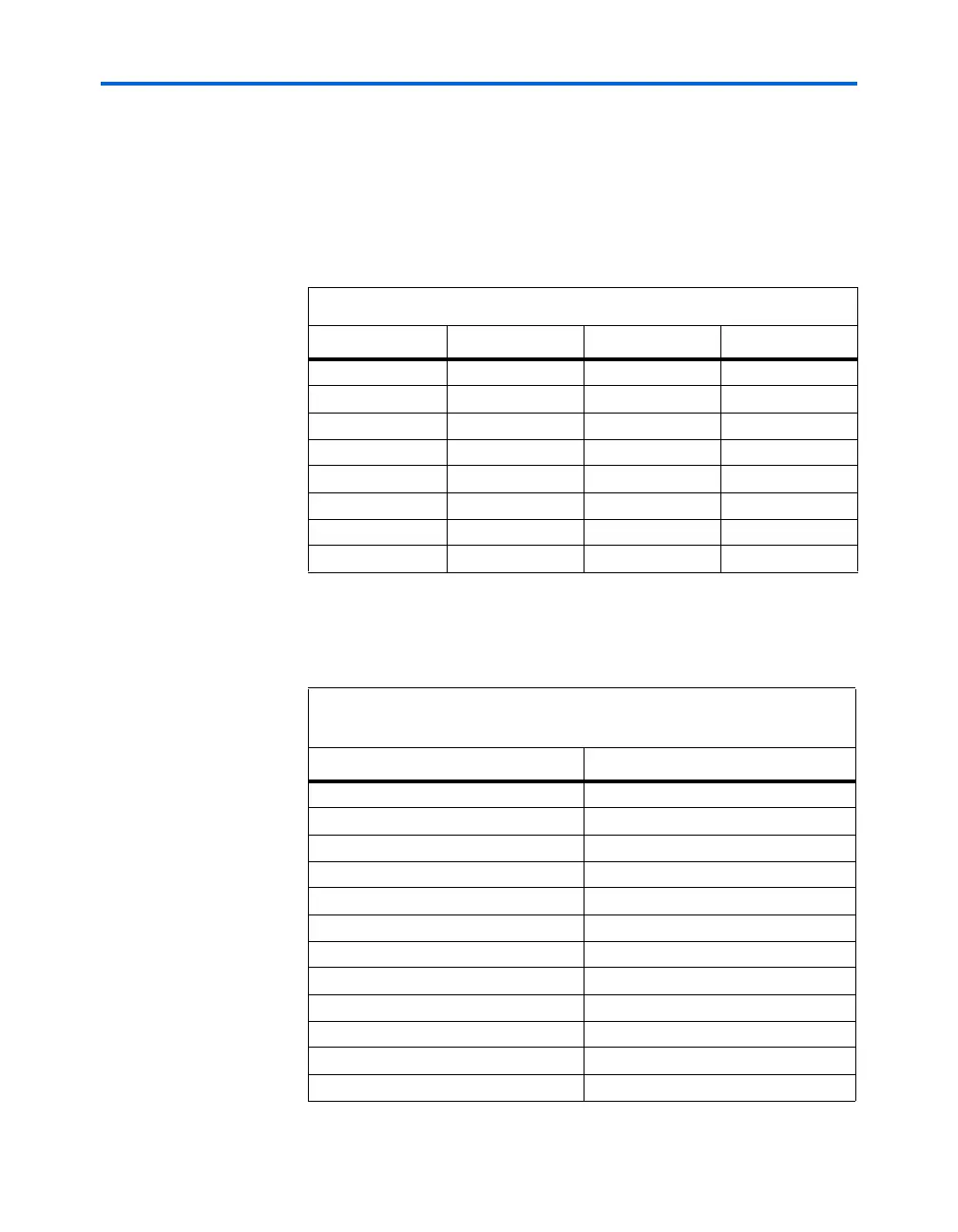

Table 2–5. Byte Enable for M-RAM Blocks Notes (1), (2)

byteena datain × 18 datain × 36 datain × 72

[0] = 1 [8..0] [8..0] [8..0]

[1] = 1 [17..9] [17..9] [17..9]

[2] = 1 – [26..18] [26..18]

[3] = 1 – [35..27] [35..27]

[4] = 1 – – [44..36]

[5] = 1 – – [53..45]

[6] = 1 – – [62..54]

[7] = 1 – – [71..63]

Notes to Ta b le 2 – 5 :

(1) Any combination of byte enables is possible.

(2) Byte enables can be used in the same manner with 8-bit words, that is, in ×16, × 32,

and ×64 modes.

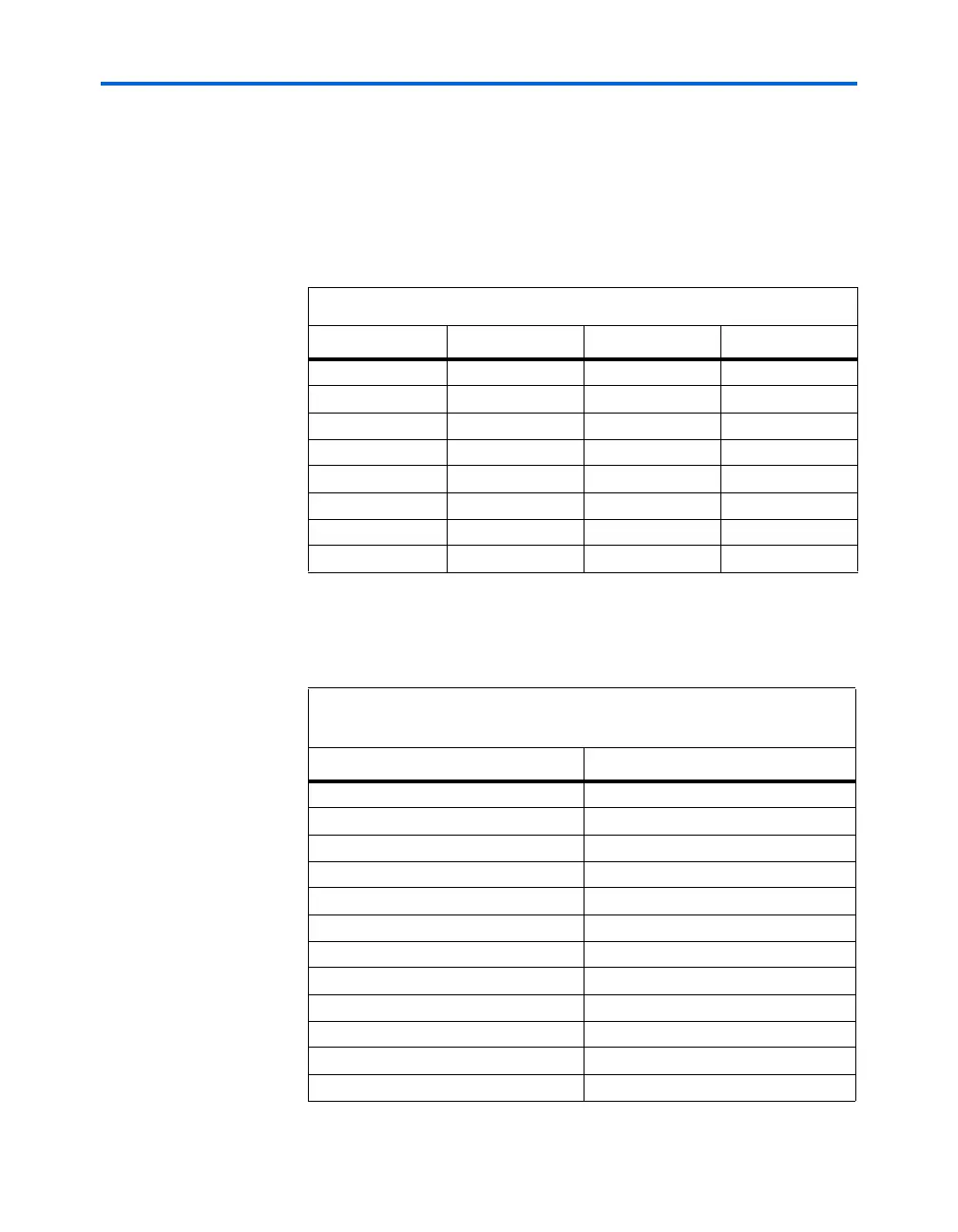

Table 2–6. M-RAM Combined Byte Selection for × 144 Mode (Part 1 of 2),

Notes (1), (2)

byteena_a datain × 144

[0] = 1 [8..0]

[1] = 1 [17..9]

[2] = 1 [26..18]

[3] = 1 [35..27]

[4] = 1 [44..36]

[5] = 1 [53..45]

[6] = 1 [62..54]

[7] = 1 [71..63]

[8] = 1 [80..72]

[9] = 1 [89..81]

[10] = 1 [98..90]

[11] = 1 [107..99]

Loading...

Loading...