UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 142 of 523

NXP Semiconductors

UM10462

Chapter 8: LPC11U3x/2x/1x Pin configuration

PIO0_16/AD5/

CT32B1_MAT3/WAKEUP

26 40 53

[6]

I; PU I/O PIO0_16 — General purpose digital input/output pin. In

Deep power-down mode, this pin functions as the

WAKEUP pin with 20 ns glitch filter. Pull this pin HIGH

externally to enter Deep power-down mode. Pull this pin

LOW to exit Deep power-down mode. A LOW-going pulse

as short as 50 ns wakes up the part.

-IAD5 — A/D converter, input 5.

-OCT32B1_MAT3 — Match output 3 for 32-bit timer 1.

PIO0_17/RTS

/

CT32B0_CAP0/SCLK

30 45 60

[3]

I; PU I/O PIO0_17 — General purpose digital input/output pin.

-ORTS

— Request To Send output for USART.

-ICT32B0_CAP0 — Capture input 0 for 32-bit timer 0.

-I/OSCLK — Serial clock input/output for USART in

synchronous mode.

PIO0_18/RXD/

CT32B0_MAT0

31 46 61

[3]

I; PU I/O PIO0_18 — General purpose digital input/output pin.

-IRXD — Receiver input for USART. Used in UART ISP

mode.

-OCT32B0_MAT0 — Match output 0 for 32-bit timer 0.

PIO0_19/TXD/

CT32B0_MAT1

32 47 62

[3]

I; PU I/O PIO0_19 — General purpose digital input/output pin.

-OTXD — Transmitter output for USART. Used in UART ISP

mode.

-OCT32B0_MAT1 — Match output 1 for 32-bit timer 0.

PIO0_20/CT16B1_CAP0 7 9 11

[3]

I; PU I/O PIO0_20 — General purpose digital input/output pin.

-ICT16B1_CAP0 — Capture input 0 for 16-bit timer 1.

PIO0_21/CT16B1_MAT0/

MOSI1

12 17 22

[3]

I; PU I/O PIO0_21 — General purpose digital input/output pin.

-OCT16B1_MAT0 — Match output 0 for 16-bit timer 1.

-I/OMOSI1 — Master Out Slave In for SSP1.

PIO0_22/AD6/

CT16B1_MAT1/MISO1

20 30 40

[6]

I; PU I/O PIO0_22 — General purpose digital input/output pin.

-IAD6 — A/D converter, input 6.

-OCT16B1_MAT1 — Match output 1 for 16-bit timer 1.

-I/OMISO1 — Master In Slave Out for SSP1.

PIO0_23/AD7 27 42 56

[6]

I; PU I/O PIO0_23 — General purpose digital input/output pin.

-IAD7 — A/D converter, input 7.

PIO1_0/CT32B1_MAT0 - - 1

[3]

I; PU I/O PIO1_0 — General purpose digital input/output pin.

-OCT32B1_MAT0 — Match output 0 for 32-bit timer 1.

PIO1_1/CT32B1_MAT1 - - 17

[3]

I; PU I/O PIO1_1 — General purpose digital input/output pin.

-OCT32B1_MAT1 — Match output 1 for 32-bit timer 1.

PIO1_2/CT32B1_MAT2 - - 34

[3]

I; PU I/O PIO1_2 — General purpose digital input/output pin.

-OCT32B1_MAT2 — Match output 2 for 32-bit timer 1.

PIO1_3/CT32B1_MAT3 - - 50

[3]

I; PU I/O PIO1_3 — General purpose digital input/output pin.

-OCT32B1_MAT3 — Match output 3 for 32-bit timer 1.

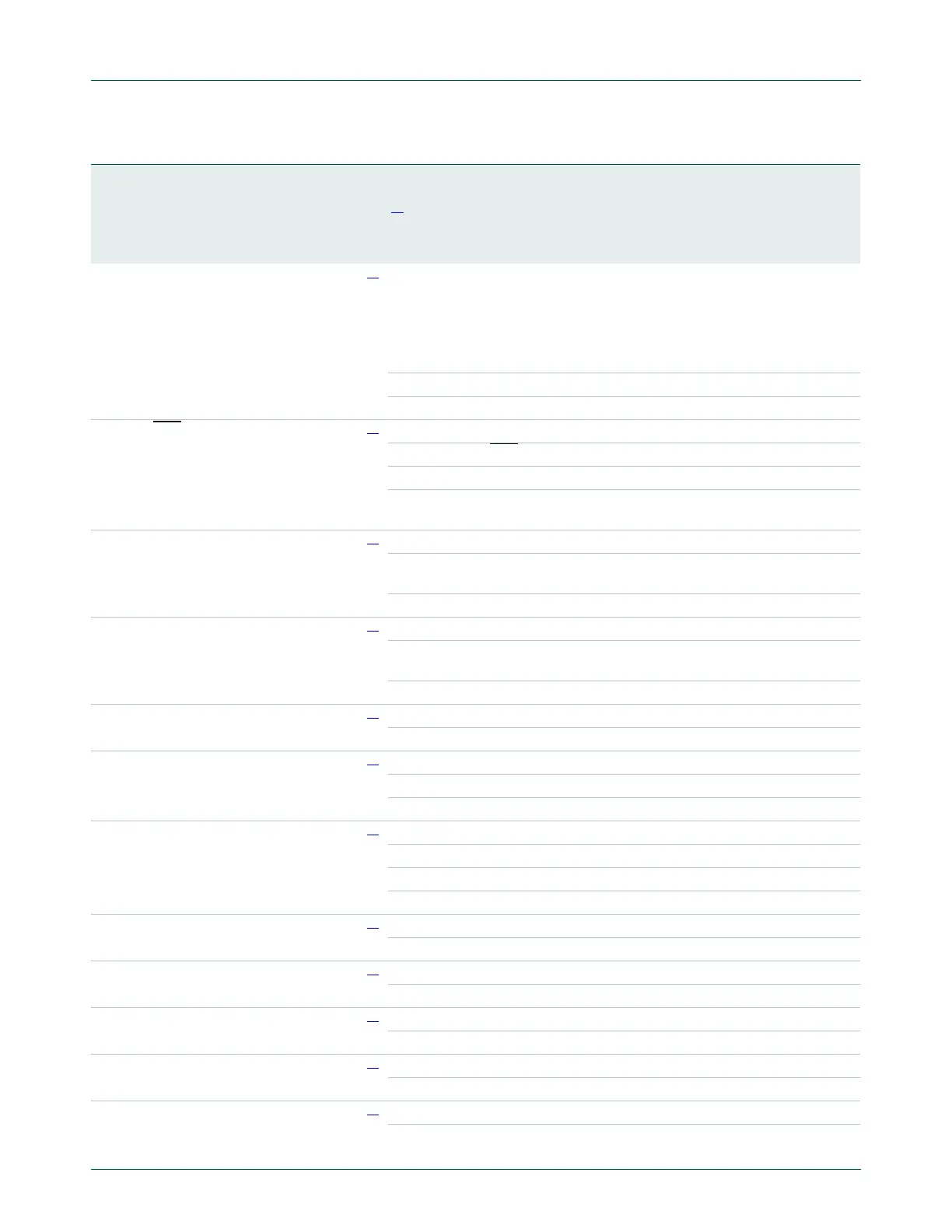

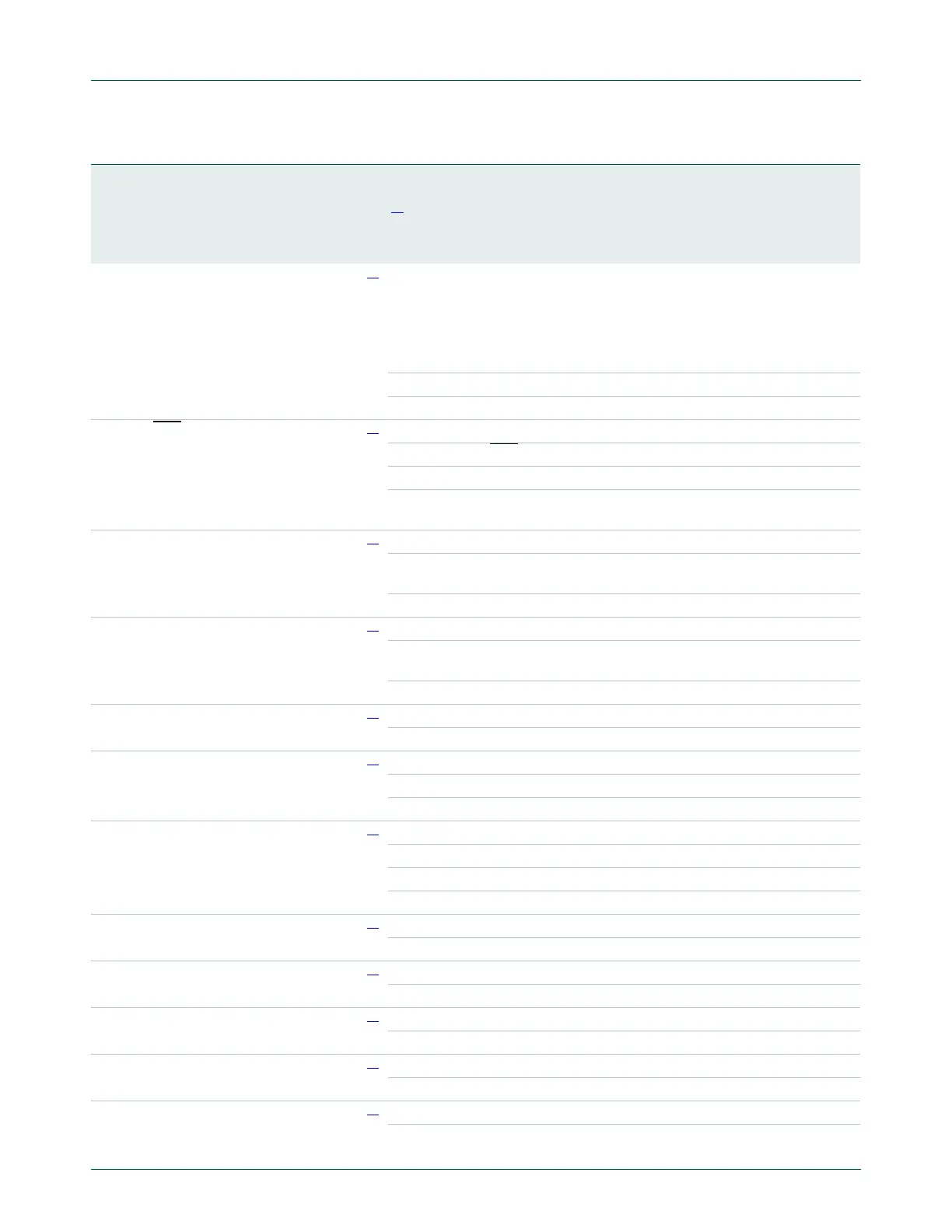

Table 134. LPC11U2x pin description

…continued

Symbol

Pin HVQFN33

Pin LQFP48

Pin LQFP64

Reset

state

[1]

Type Description

Loading...

Loading...