UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 151 of 523

NXP Semiconductors

UM10462

Chapter 8: LPC11U3x/2x/1x Pin configuration

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled; IA = inactive, no pull-up/down enabled;

F = floating; If the pins are not used, tie floating pins to ground or power to minimize power consumption.

[2] 5 V tolerant pad. RESET

functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up

from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis.

[4] I

2

C-bus pins compliant with the I

2

C-bus specification for I

2

C standard mode, I

2

C Fast-mode, and I

2

C Fast-mode Plus. The pin requires

an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines.

Open-drain configuration applies to all functions on this pin.

[5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis; includes

high-current output driver.

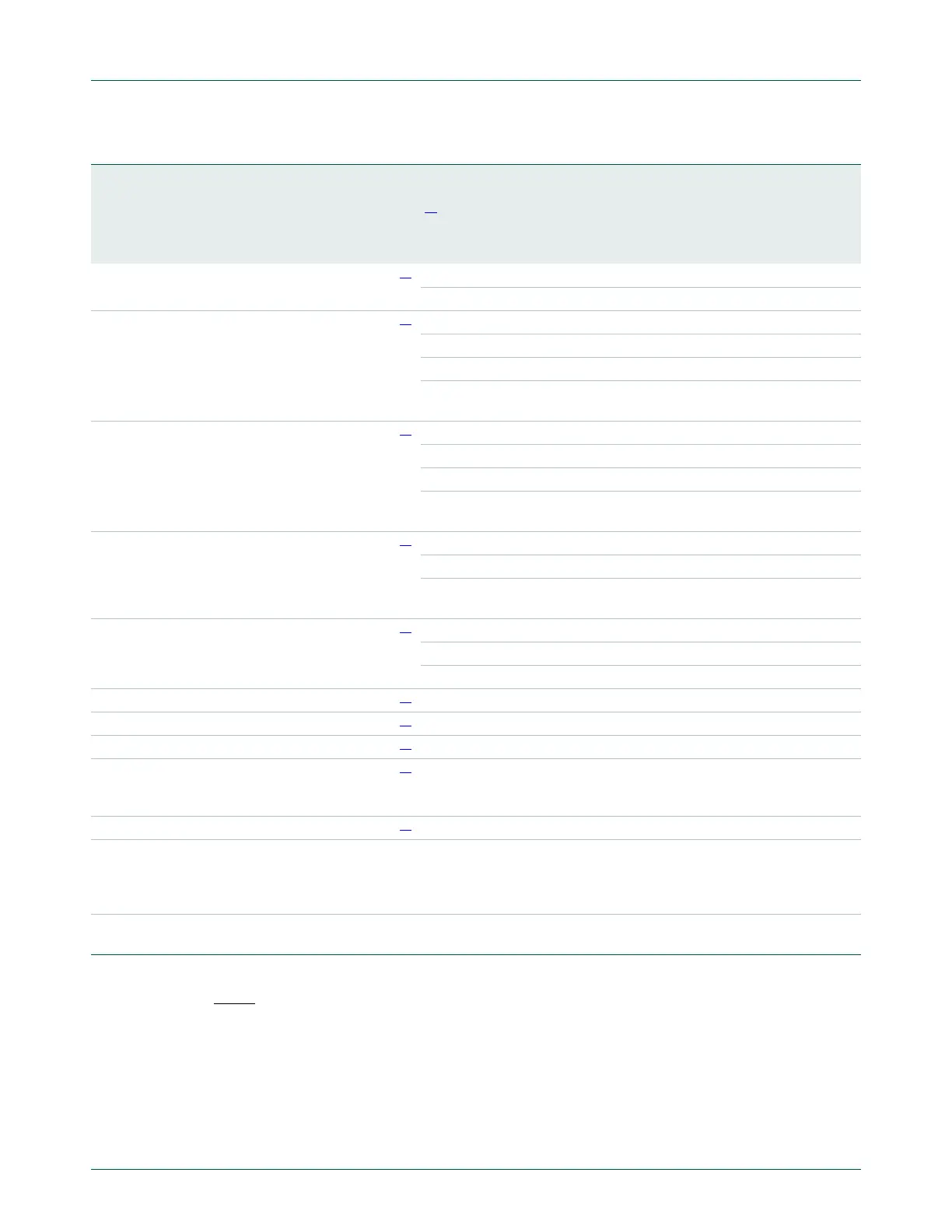

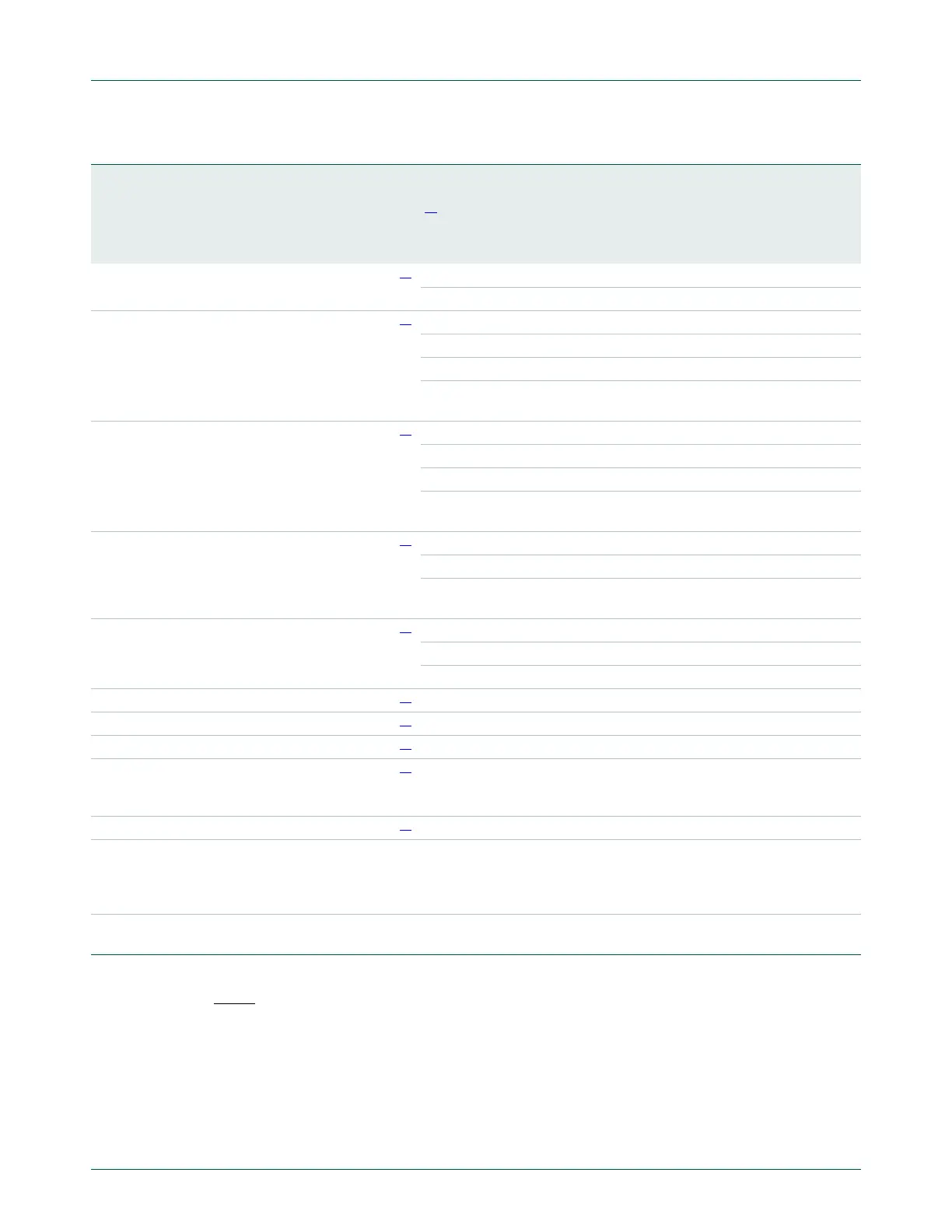

PIO1_25/CT32B0_MAT1 - A1 1 2

[3]

I; PU I/O PIO1_25 — General purpose digital input/output pin.

-OCT32B0_MAT1 — Match output 1 for 32-bit timer 0.

PIO1_26/CT32B0_MAT2/

RXD/IOH_19

-G21114

[3]

I; PU I/O PIO1_26 — General purpose digital input/output pin.

-OCT32B0_MAT2 — Match output 2 for 32-bit timer 0.

-IRXD — Receiver input for USART.

- I/O IOH_19 — I/O Handler input/output 19.

(LPC11U37HFBD64/401 only.)

PIO1_27/CT32B0_MAT3/

TXD/IOH_20

-G11215

[3]

I; PU I/O PIO1_27 — General purpose digital input/output pin.

-OCT32B0_MAT3 — Match output 3 for 32-bit timer 0.

-OTXD — Transmitter output for USART.

- I/O IOH_20 — I/O Handler input/output 20.

(LPC11U37HFBD64/401 only.)

PIO1_28/CT32B0_CAP0/

SCLK

-H72431

[3]

I; PU I/O PIO1_28 — General purpose digital input/output pin.

-ICT32B0_CAP0 — Capture input 0 for 32-bit timer 0.

- I/O SCLK — Serial clock input/output for USART in

synchronous mode.

PIO1_29/SCK0/

CT32B0_CAP1

-D73141

[3]

I; PU I/O PIO1_29 — General purpose digital input/output pin.

- I/O SCK0 — Serial clock for SSP0.

-ICT32B0_CAP1 — Capture input 1 for 32-bit timer 0.

PIO1_31 - - 25 -

[3]

I; PU I/O PIO1_31 — General purpose digital input/output pin.

USB_DM 13 G5 19 25

[7]

F-USB_DM — USB bidirectional D line.

USB_DP 14 H5 20 26

[7]

F-USB_DP — USB bidirectional D+ line.

XTALIN 4 D1 6 8

[8]

- - Input to the oscillator circuit and internal clock

generator circuits. Input voltage must not exceed

1.8 V.

XTALOUT 5 E1 7 9

[8]

- - Output from the oscillator amplifier.

V

DD

6;

29

B4;

E2

8;

44

10;

33;

48;

58

- - Supply voltage to the internal regulator, the external

rail, and the ADC. Also used as the ADC reference

voltage.

V

SS

33 B5;

D2

5;

41

7;

54

- - Ground.

Table 135. LPC11U3x pin description

…continued

Symbol

Pin HVQFN33

Pin TFBGA48

Pin LQFP48

Pin LQFP64

Reset

state

[1]

Type Description

Loading...

Loading...