UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 268 of 523

NXP Semiconductors

UM10462

Chapter 12: LPC11U3x/2x/1x USART

12.5.22 USART Synchronous mode control register

SYNCCTRL register controls the synchronous mode. When this mode is in effect, the

USART generates or receives a bit clock on the SCLK pin and applies it to the transmit

and receive shift registers. Synchronous mode should not be used with smart card mode.

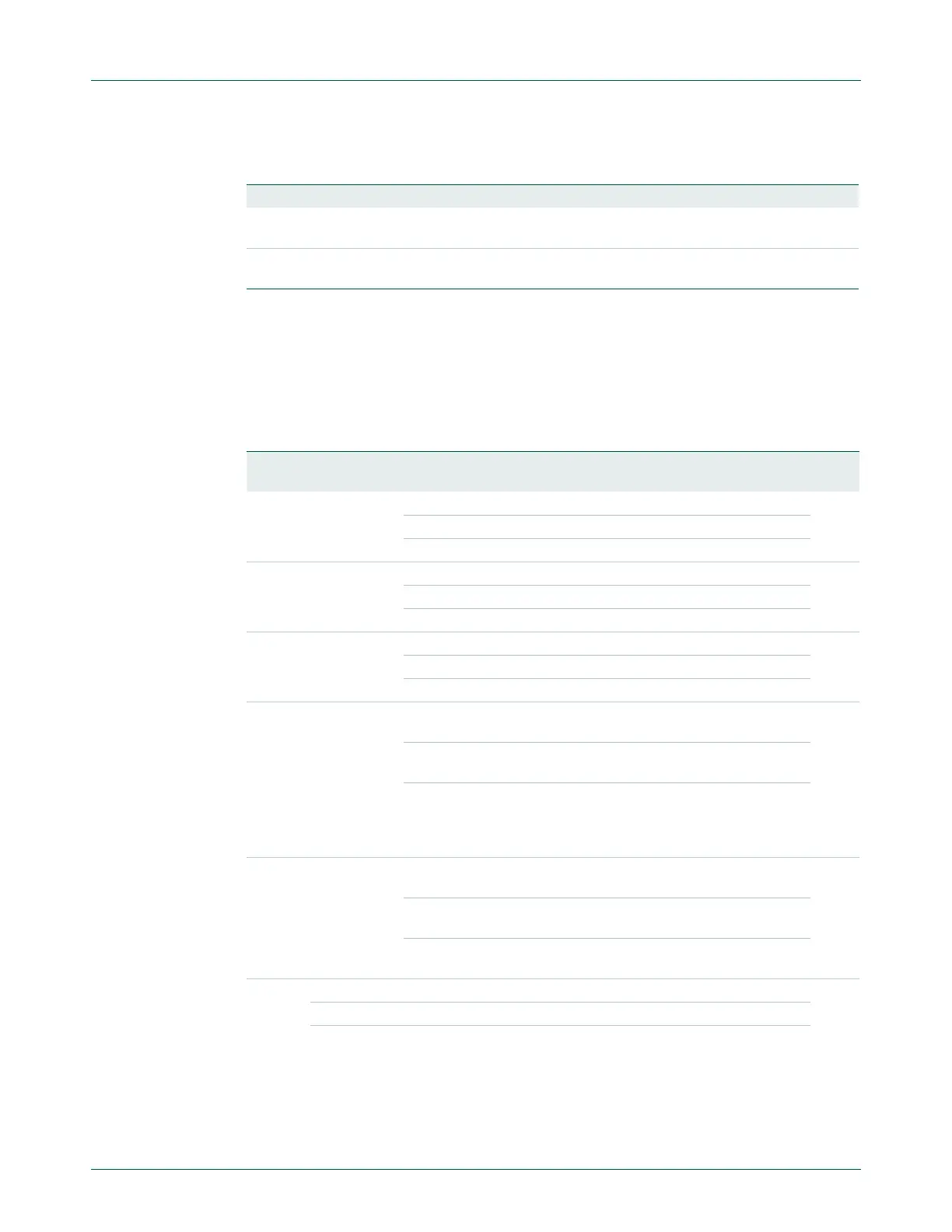

Table 255. USART RS-485 Delay value register (RS485DLY - address 0x4000 8054) bit

description

Bit Symbol Description Reset value

7:0 DLY Contains the direction control (RTS or DTR) delay value. This

register works in conjunction with an 8-bit counter.

0x00

31:8 - Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

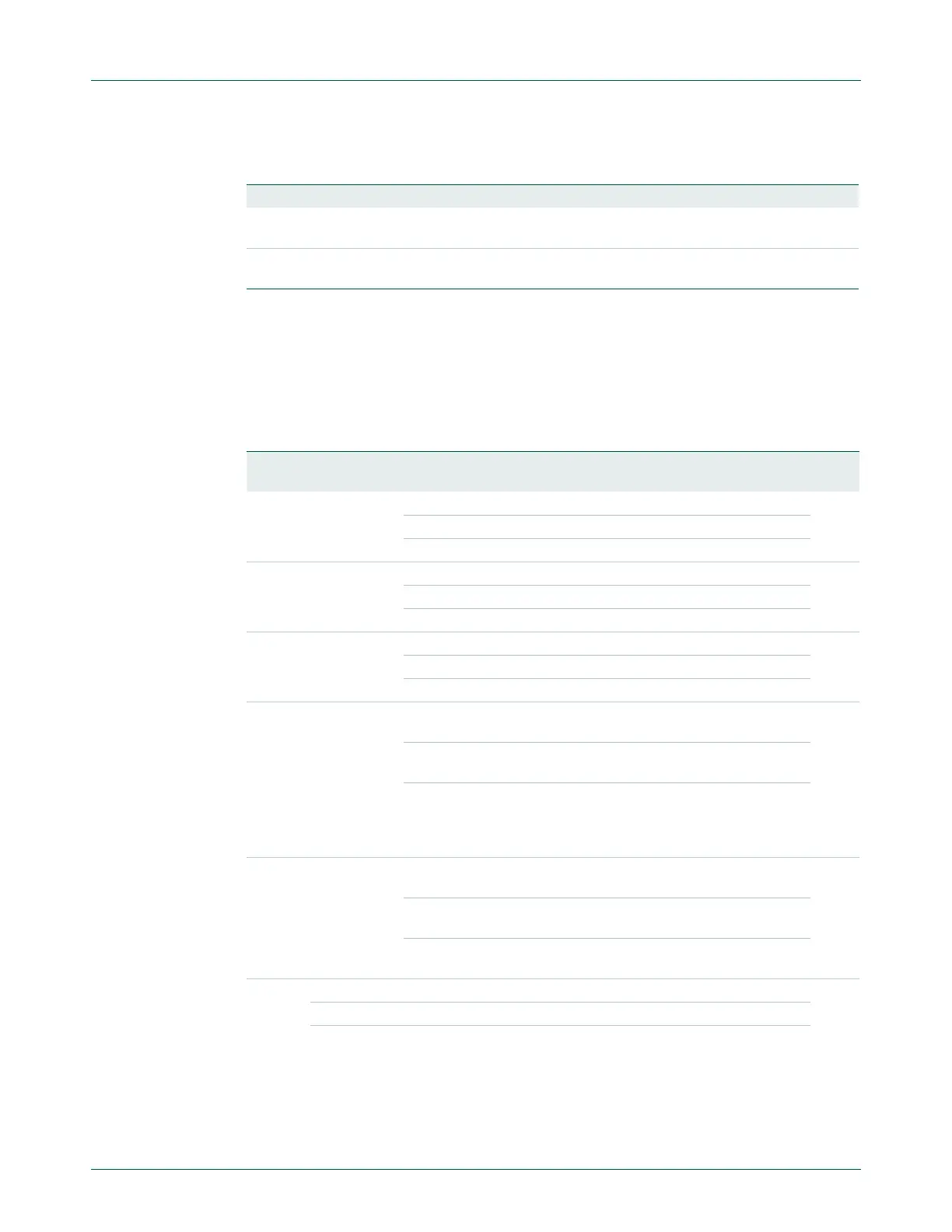

Table 256. USART Synchronous mode control register (SYNCCTRL - address 0x4000 8058)

bit description

Bit Symbol Value Description Reset

value

0 SYNC Enables synchronous mode. 0

0 Disabled

1 Enabled

1 CSRC Clock source select. 0

0 Synchronous slave mode (SCLK in)

1 Synchronous master mode (SCLK out)

2 FES Falling edge sampling. 0

0 RxD is sampled on the rising edge of SCLK

1 RxD is sampled on the falling edge of SCLK

3 TSBYPASS Transmit synchronization bypass in synchronous slave

mode.

0

0 The input clock is synchronized prior to being used in

clock edge detection logic.

1 The input clock is not synchronized prior to being used

in clock edge detection logic. This allows for a high er

input clock rate at the expense of potential

metastability.

4 CSCEN Continuous master clock enable (used only when

CSRC is 1)

0

0 SCLK cycles only when characters are being sent on

TxD

1 SCLK runs continuously (characters can be received

on RxD independently from transmission on TxD)

5 SSDIS Start/stop bits 0

0 Send start and stop bits as in other modes.

1 Do not send start/stop bits.

Loading...

Loading...