UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 449 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

Sufficient priority means the exception has greater priority than any limit set by the mask

register, see Section 24–24.3.1.3.6

. An exception with less priority than this is pending but

is not handled by the processor.

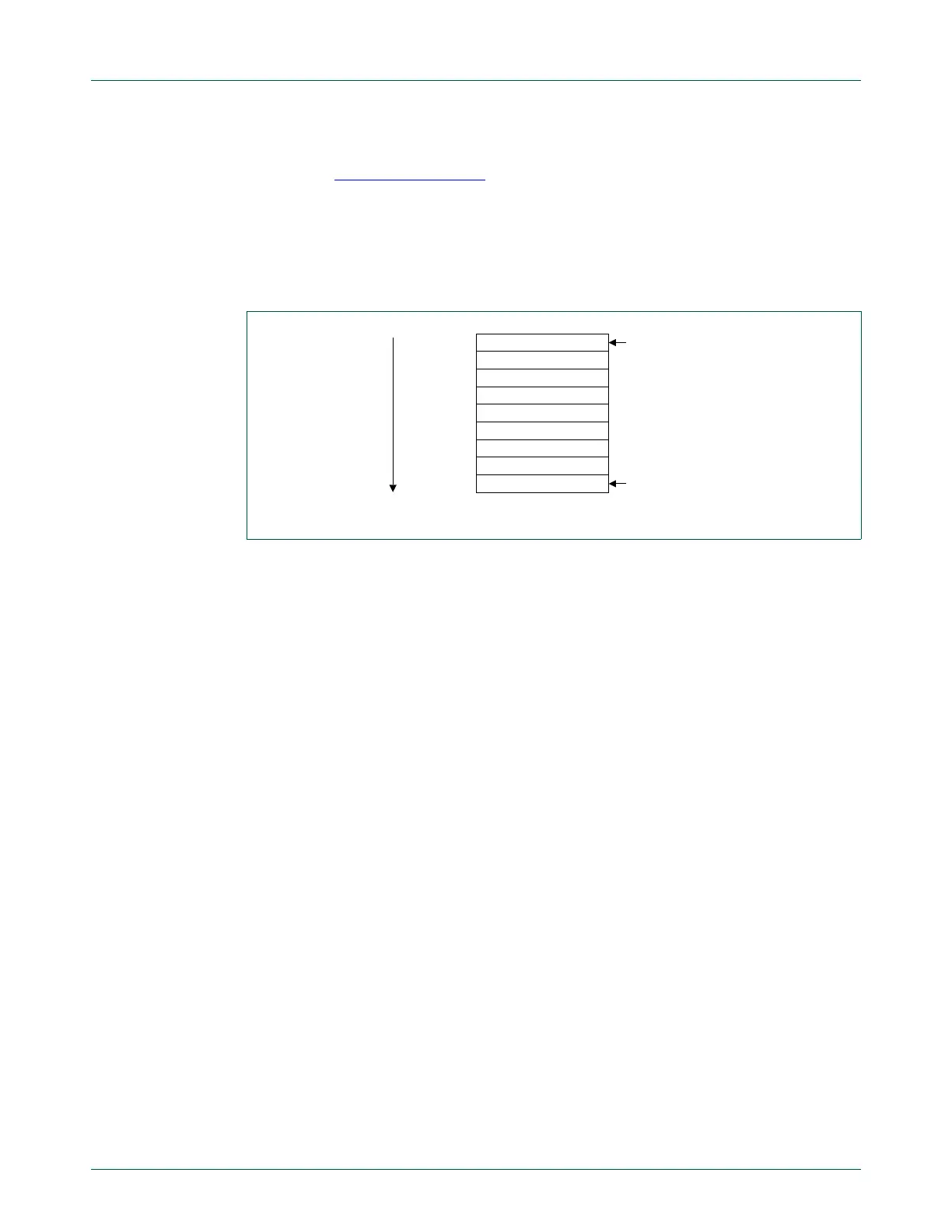

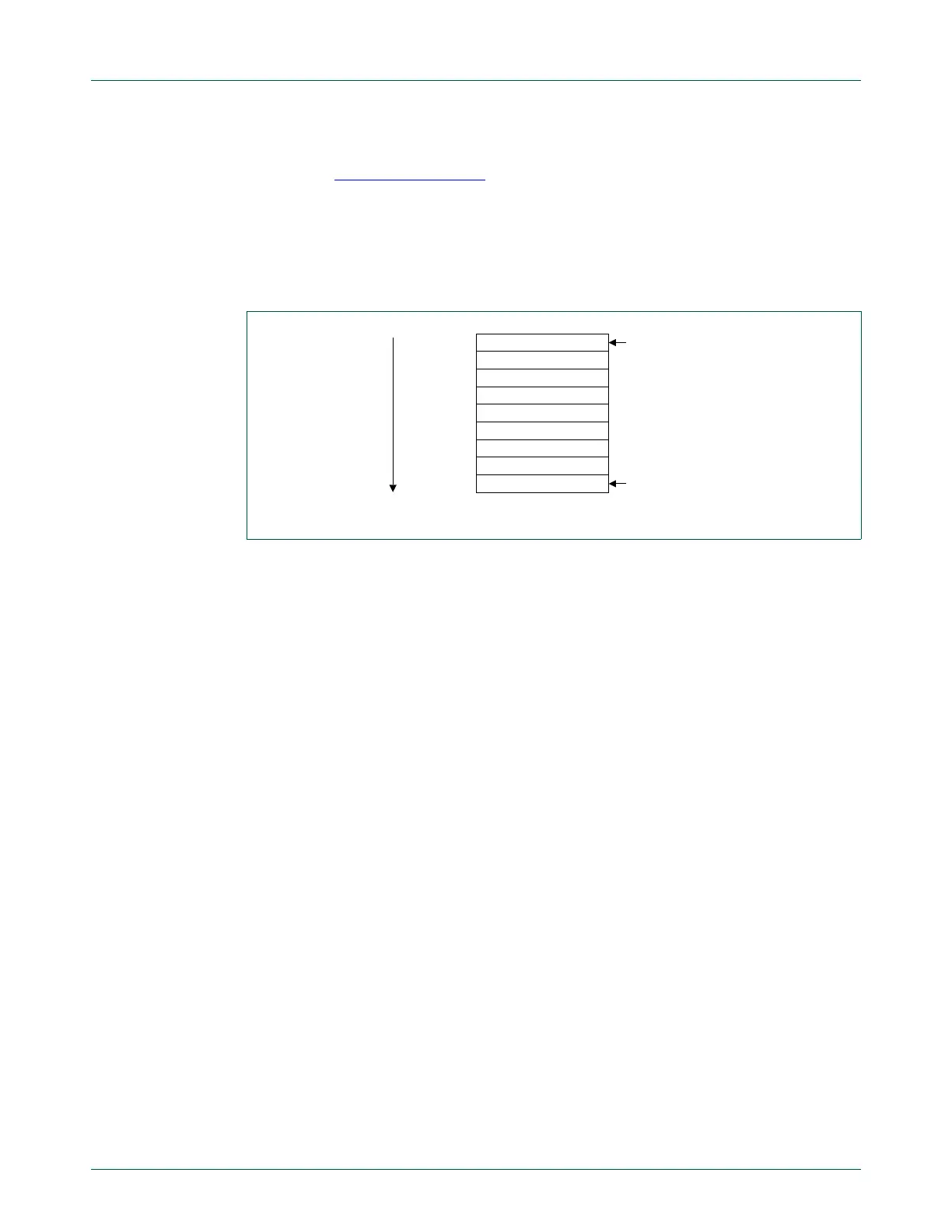

When the processor takes an exception, unless the exception is a tail-chained or a

late-arriving exception, the processor pushes information onto the current stack. This

operation is referred to as stacking and the structure of eight data words is referred as a

stack frame. The stack frame contains the following information:

Immediately after stacking, the stack pointer indicates the lowest address in the stack

frame. The stack frame is aligned to a double-word address.

The stack frame includes the return address. This is the address of the next instruction in

the interrupted program. This value is restored to the PC at exception return so that the

interrupted program resumes.

The processor performs a vector fetch that reads the exception handler start address from

the vector table. When stacking is complete, the processor starts executing the exception

handler. At the same time, the processor writes an EXC_RETURN value to the LR. This

indicates which stack pointer corresponds to the stack frame and what operation mode

the processor was in before the entry occurred.

If no higher priority exception occurs during exception entry, the processor starts

executing the exception handler and automatically changes the status of the

corresponding pending interrupt to active.

If another higher priority exception occurs during exception entry, the processor starts

executing the exception handler for this exception and does not change the pending

status of the earlier exception. This is the late arrival case.

24.3.3.6.2 Exception return

Exception return occurs when the processor is in Handler mode and execution of one of

the following instructions attempts to set the PC to an EXC_RETURN value:

• a

POP

instruction that loads the PC

• a

BX

instruction using any register.

The processor saves an EXC_RETURN value to the LR on exception entry. The

exception mechanism relies on this value to detect when the processor has completed an

exception handler. Bits[31:4] of an EXC_RETURN value are

0xFFFFFFF

. When the

processor loads a value matching this pattern to the PC it detects that the operation is a

Fig 81. Exception entry stack contents

63SRLQWVKHUHEHIRUHLQWHUUXSW

[365

3&

/5

5

5

5

5

5

SUHYLRXV!

63SRLQWVKHUHDIWHULQWHUUXSW

63[&

63[

63[

63[

63[&

63[

63[

63[

'HFUHDVLQJ

PHPRU\

DGGUHVV

Loading...

Loading...