UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 469 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

24.4.5.1.4 Examples

The following shows two instructions that add a 64-bit integer contained in R0 and R1 to

another 64-bit integer contained in R2 and R3, and place the result in R0 and R1.

64-bit addition:

ADDS R0, R0, R2 ; add the least significant words

ADCS R1, R1, R3 ; add the most significant words with carry

Multiword values do not have to use consecutive registers. The following shows

instructions that subtract a 96-bit integer contained in R1, R2, and R3 from another

contained in R4, R5, and R6. The example stores the result in R4, R5, and R6.

96-bit subtraction:

SUBS R4, R4, R1 ; subtract the least significant words

SBCS R5, R5, R2 ; subtract the middle words with carry

SBCS R6, R6, R3 ; subtract the most significant words with carry

The following shows the RSBS instruction used to perform a 1's complement of a single

register.

Arithmetic negation:

RSBS R7, R7, #0 ; subtract R7 from zero

24.4.5.2 AND, ORR, EOR, and BIC

Logical AND, OR, Exclusive OR, and Bit Clear.

24.4.5.2.1 Syntax

ANDS {Rd,} Rn, Rm

ORRS {Rd,} Rn, Rm

EORS {Rd,} Rn, Rm

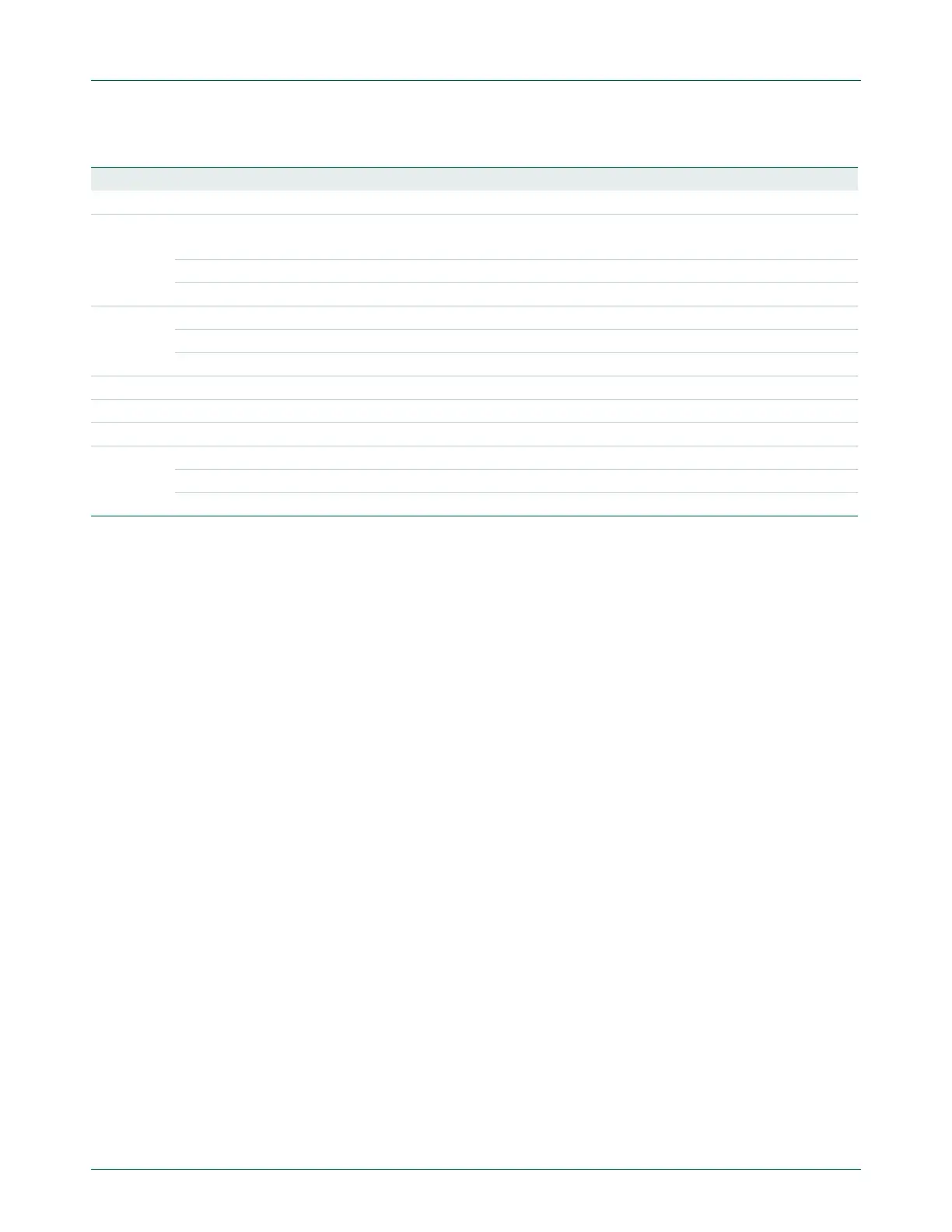

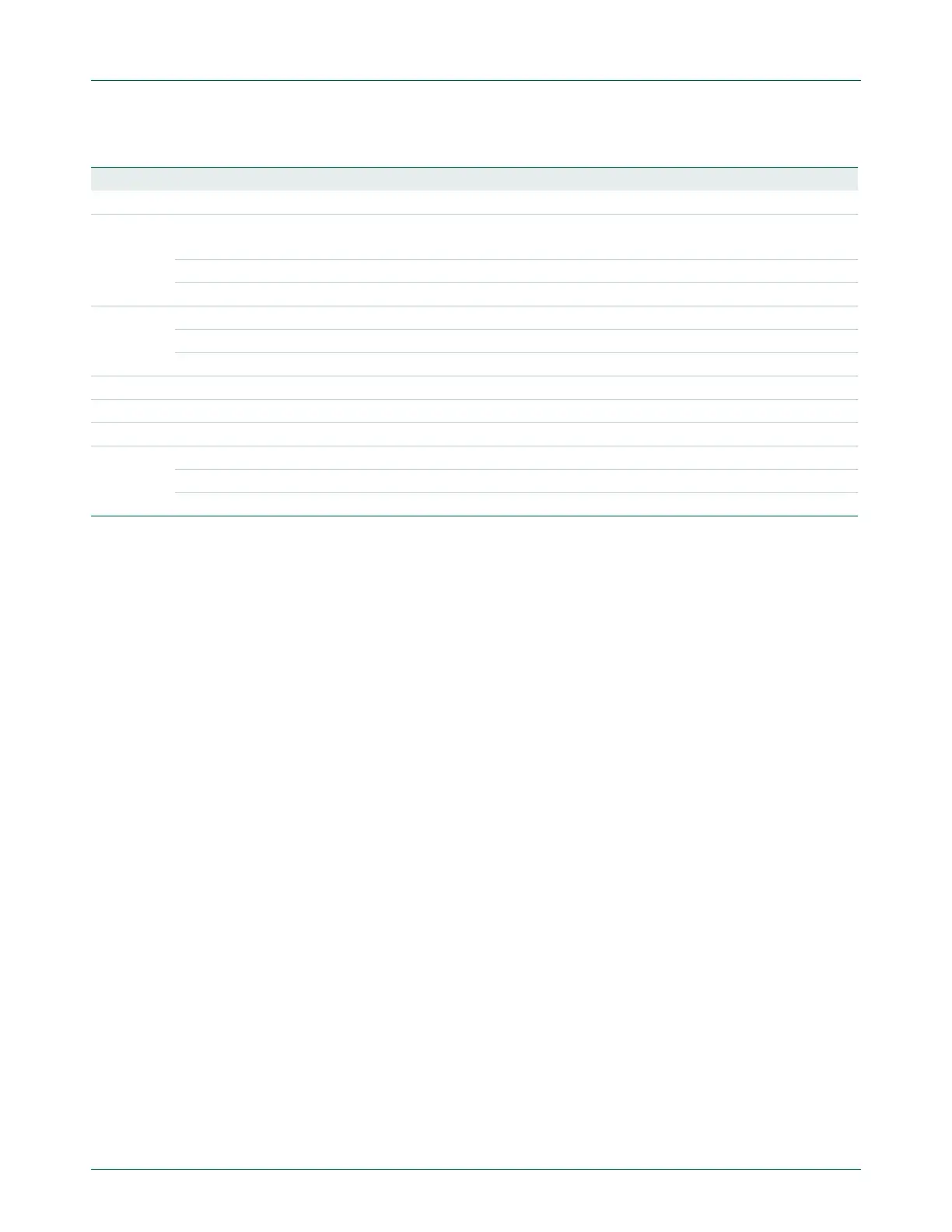

Table 429. ADC, ADD, RSB, SBC and SUB operand restrictions

Instruction Rd Rn Rm imm Restrictions

ADCS R0-R7 R0-R7 R0-R7 - Rd and Rn must specify the same register.

ADD R0-R15 R0-R15 R0-PC - Rd and Rn must specify the same register.

Rn and Rm must not both specify PC.

R0-R7 SP or PC - 0-1020 Immediate value must be an integer multiple of four.

SP SP - 0-508 Immediate value must be an integer multiple of four.

ADDS R0-R7 R0-R7 - 0-7 -

R0-R7 R0-R7 - 0-255 Rd and Rn must specify the same register.

R0-R7 R0-R7 R0-R7 - -

RSBS R0-R7 R0-R7 - - -

SBCS R0-R7 R0-R7 R0-R7 - Rd and Rn must specify the same register.

SUB SP SP - 0-508 Immediate value must be an integer multiple of four.

SUBS R0-R7 R0-R7 - 0-7 -

R0-R7 R0-R7 - 0-255 Rd and Rn must specify the same register.

R0-R7 R0-R7 R0-R7 - -

Loading...

Loading...