3–24 Altera Corporation

Stratix Device Handbook, Volume 2 June 2006

DDR Memory Support Overview

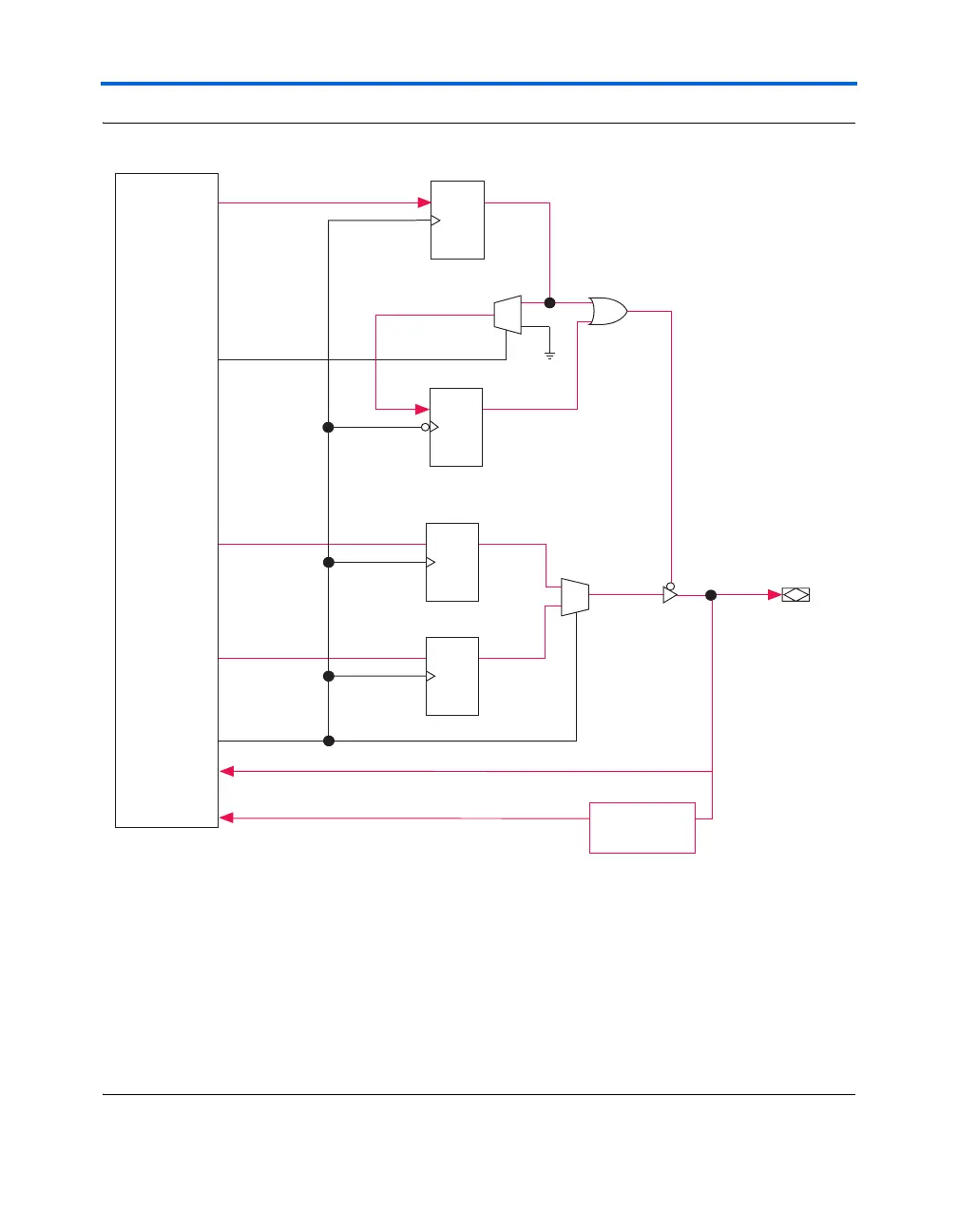

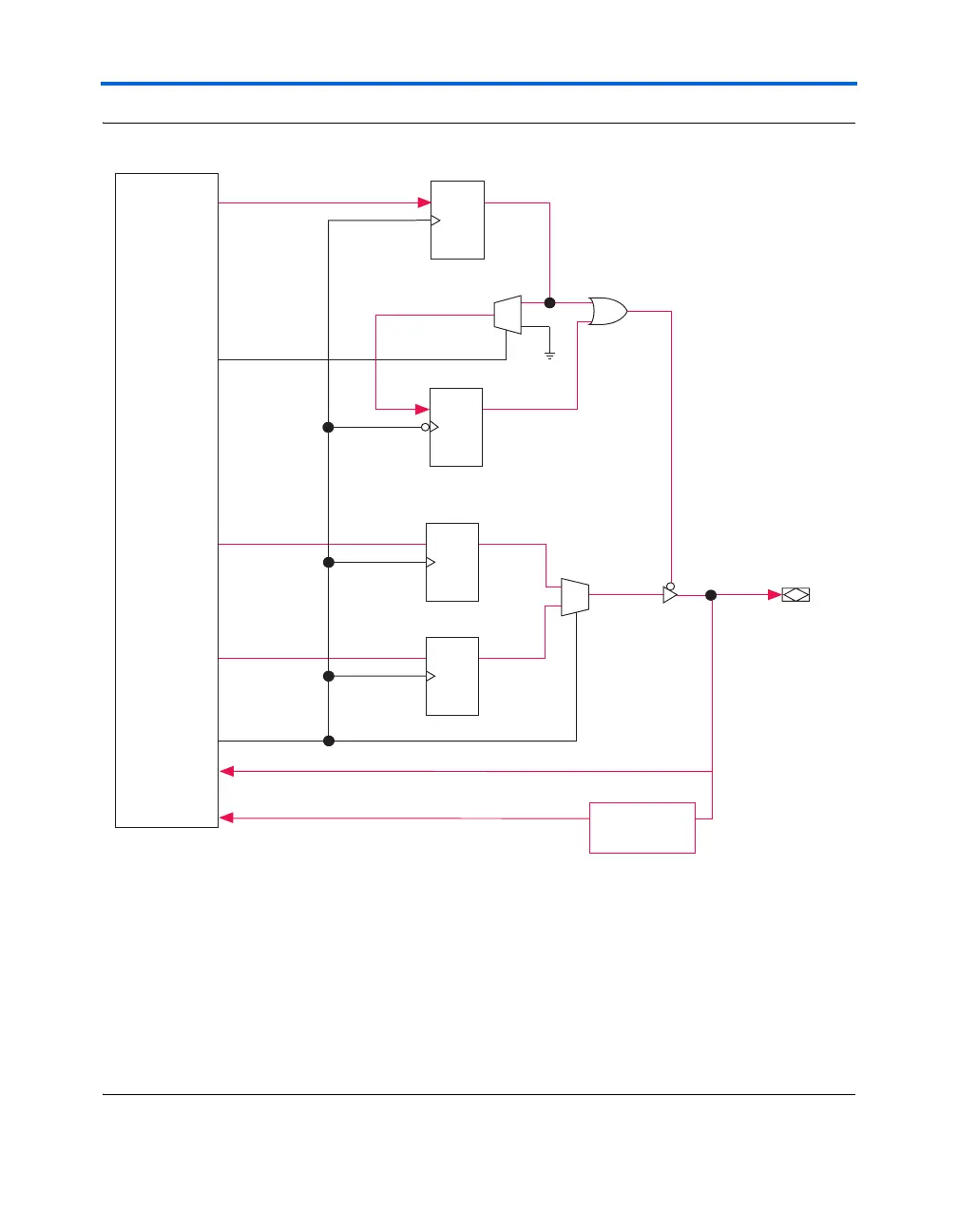

Figure 3–13. DQS Configuration in Stratix & Stratix GX IOE Note (1)

Notes to Figure 3–13:

(1) You can use the altdqs megafunction to generate the DQS signals.

(2) The OE signal is active low, but the Quartus II software implements this as active high and automatically adds an

inverter before OE register A

OE

during compilation.

(3) The select line can be chosen in the altdqs MegaWizard Plug-In Manager.

(4) The datain_l and datain_h pins are usually connected to V

CC

and ground, respectively.

(5) DQS postamble handling is not shown in this diagram. For more information, see AN 342: Interfacing DDR SDRAM

with Stratix & Stratix GX Devices.

(6) This undelayed DQS signal goes to the LE for the soft postamble circuitry.

(7) You must invert this signal before it reaches the DQ IOE. This signal is automatically inverted if you use the altdq

megafunction to generate the DQ signals. Connect this port to the inclock port in the altdq megafunction.

(8) DQS phase-shift circuitry is only available on DQS pins.

DQ

DFF

DQ

DFF

0

1

Output Register B

O

Output Register A

O

OE Register B

OE

OE Register A

OE

DQ

DFF

DQ

DFF

OR2

TRI

DQS Pin

(5

Logic Array

system clock

datain_l

(4)

datain_h

(3)

OE

(3)

combout

(7)

(2)

0

1

DQS Phase

Shift Circuitry

(8)

undelayed DQS

(6)

Loading...

Loading...