Altera Corporation 7–9

September 2004 Stratix Device Handbook, Volume 2

Implementing High Performance DSP Functions in Stratix & Stratix GX Devices

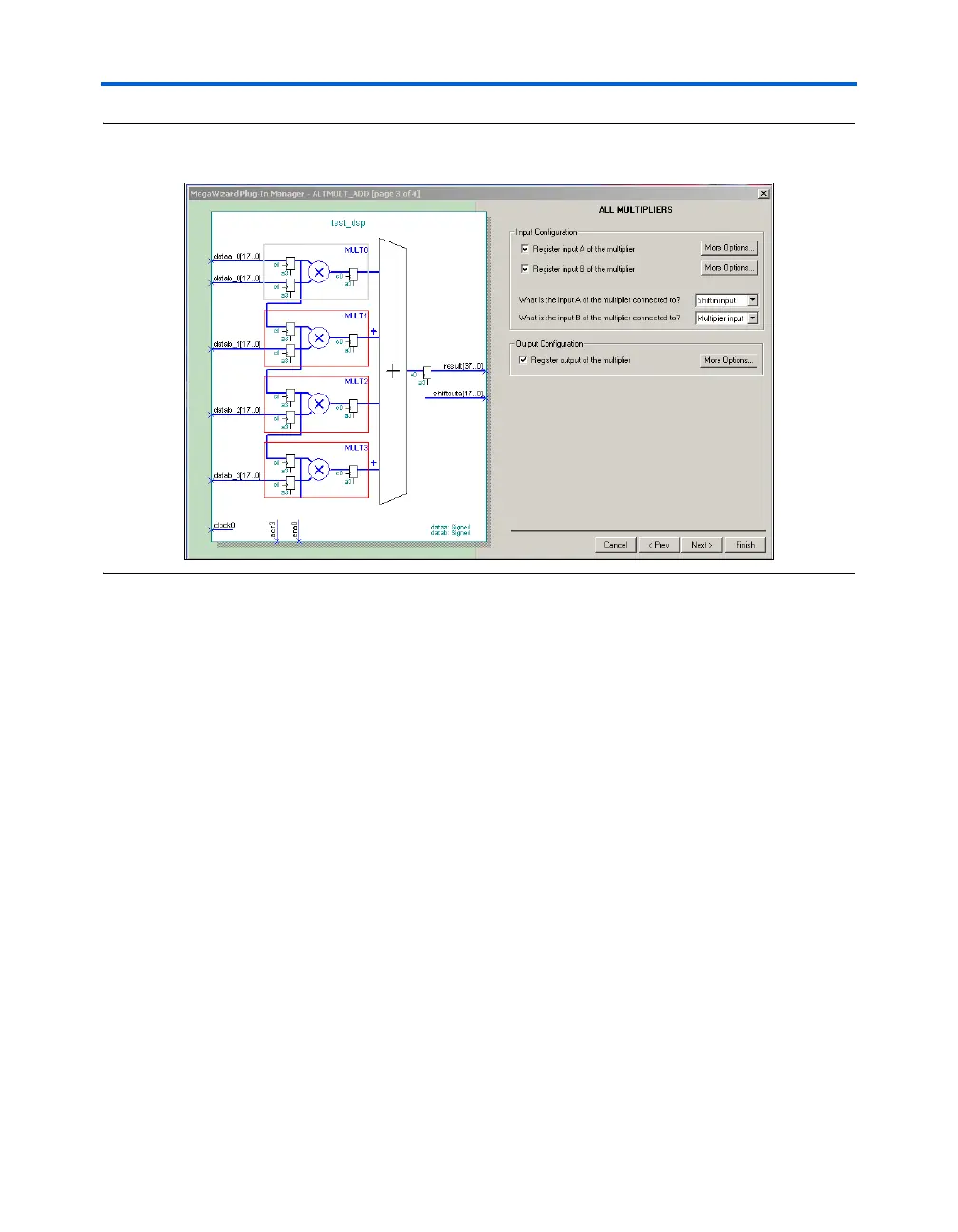

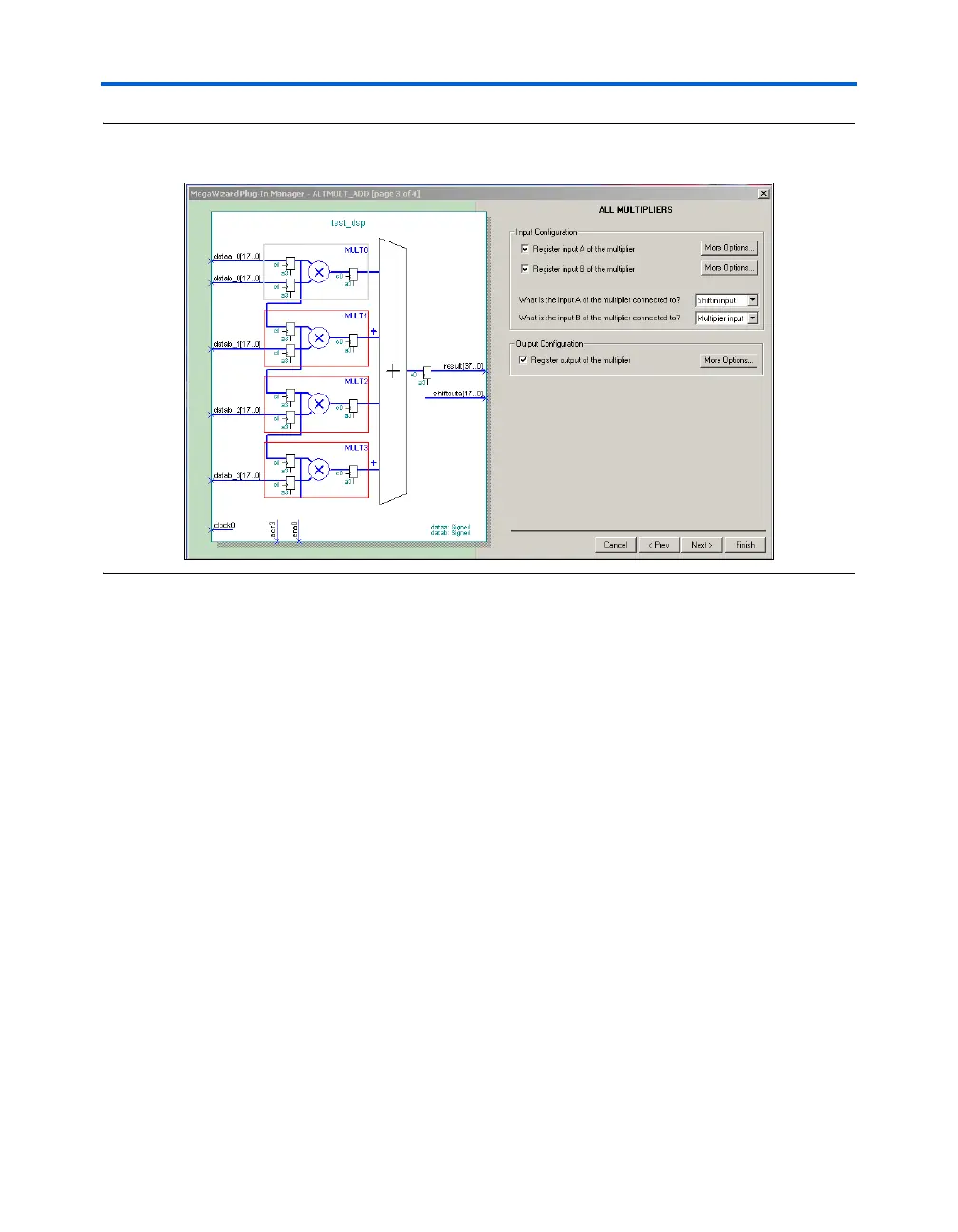

Figure 7–4. Quartus II Software View of MegaWizard Implementation of a DSP Block in Four-Multipliers

Adder Mode

Each input register of the DSP block provides a shiftout output that

connects to the shiftin input of the adjacent input register of the same DSP

block. The registers on the boundaries of a DSP block also connect to the

registers of adjacent DSP blocks through the use of shiftin/shiftout

connections. These connections create register chains spanning multiple

DSP blocks, which makes it easy to increase the length of FIR filters.

Figure 7–5 shows two DSP blocks connected to create an 8-tap FIR filter.

Filters with more taps can be implemented by connecting DSP blocks in

a similar manner, provided sufficient DSP blocks are available in the

device.

1 Adding the outputs of the two DSP blocks requires an external

adder which can be implemented using logic cells.

The input data can be fed directly or by using the shiftout/shiftin chains,

which allow a single input to shift down the register chain inside the DSP

block. The input to each of the registers has a multiplexer, hence, the data

can be fed either from outside the DSP block or the preceding register.

This can be selected from the MegaWizard

®

in the Quartus

®

II software,

as shown in Figure 7–4. The example in Figure 7–5 uses the

shiftout/shiftin flip-flop chains where the multiplexers are configured to

use these chains. In this example, the flip-flops inside the DSP blocks

serve as the taps of the FIR filter.

Loading...

Loading...