UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 155 of 523

NXP Semiconductors

UM10462

Chapter 9: LPC11U3x/2x/1x GPIO

The GPIO interrupt registers are listed in Table 137 and Section 9.5.1

• The GPIO GROUP0 interrupt block at address 0x4005 C000. Registers in this block

allow to configure any pin on port 0 and 1 to contribute to a combined interrupt. The

GPIO GROUP0 registers are listed in Table 138

and Section 9.5.2.

• The GPIO GROUP1 interrupt block at address 0x4006 0000. Registers in this block

allow to configure any pin on port 0 and 1 to contribute to a combined interrupt. The

GPIO GROUP1 registers are listed in Table 139

and Section 9.5.2.

• The GPIO port block at address 0x5000 0000. Registers in this block allow to read

and write to port pins and configure port pins as inputs or outputs.The GPIO port

registers are listed in Table 140

and Section 9.5.3.

Note: In all GPIO registers, bits that are not shown are reserved.

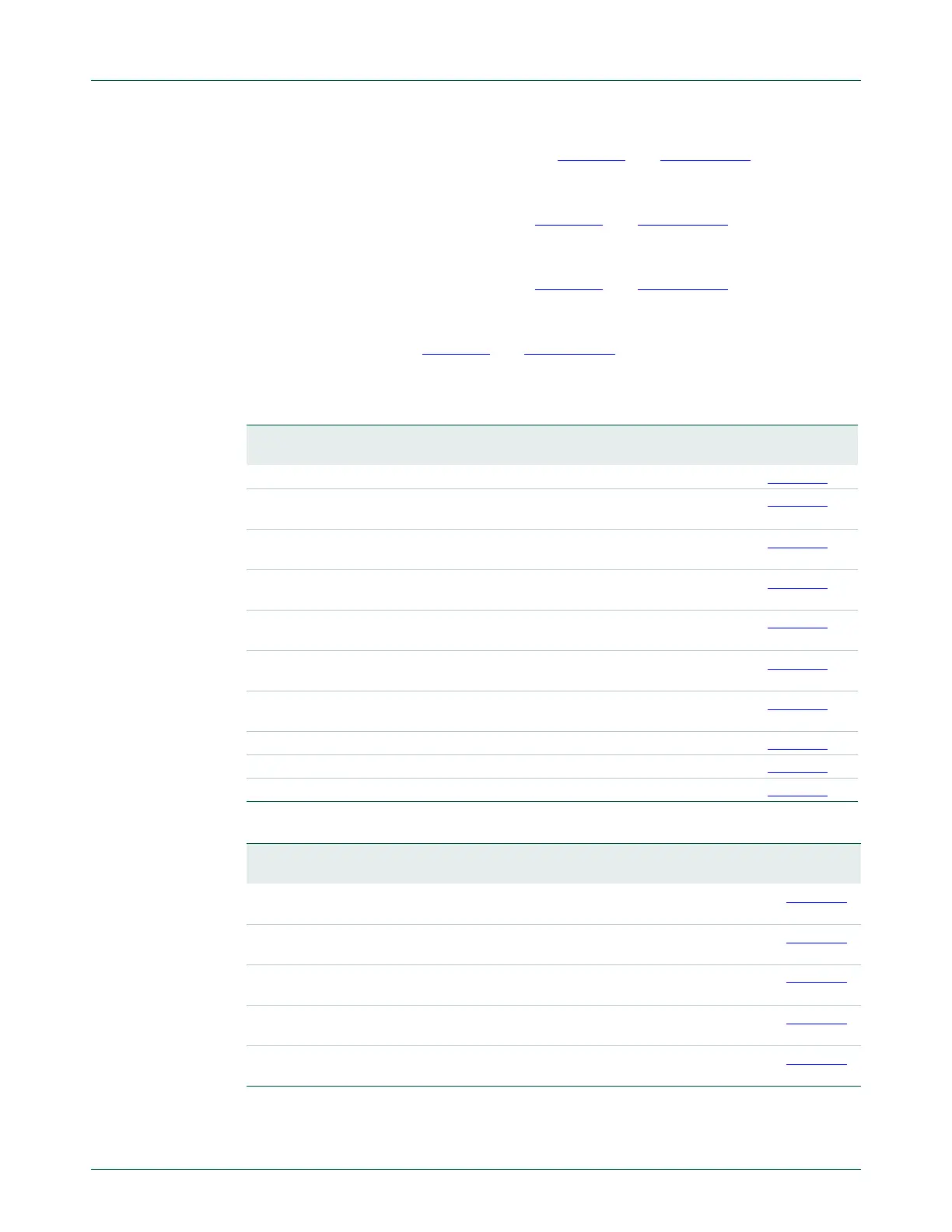

Table 137. Register overview: GPIO pin interrupts (base address: 0x4004 C000)

Name Access Address

offset

Description Reset

value

Reference

ISEL R/W 0x000 Pin Interrupt Mode register 0 Table 141

IENR R/W 0x004 Pin interrupt level (rising edge) interrupt

enable register

0 Table 142

SIENR WO 0x008 Pin interrupt level (rising edge) interrupt set

register

NA Table 143

CIENR WO 0x00C Pin interrupt level (rising edge interrupt) clear

register

NA Table 144

IENF R/W 0x010 Pin interrupt active level (falling edge)

interrupt enable register

0 Table 145

SIENF WO 0x014 Pin interrupt active level (falling edge)

interrupt set register

NA Table 146

CIENF WO 0x018 Pin interrupt active level (falling edge)

interrupt clear register

NA Table 147

RISE R/W 0x01C Pin interrupt rising edge register 0 Table 148

FALL R/W 0x020 Pin interrupt falling edge register 0 Table 149

IST R/W 0x024 Pin interrupt status register 0 Table 150

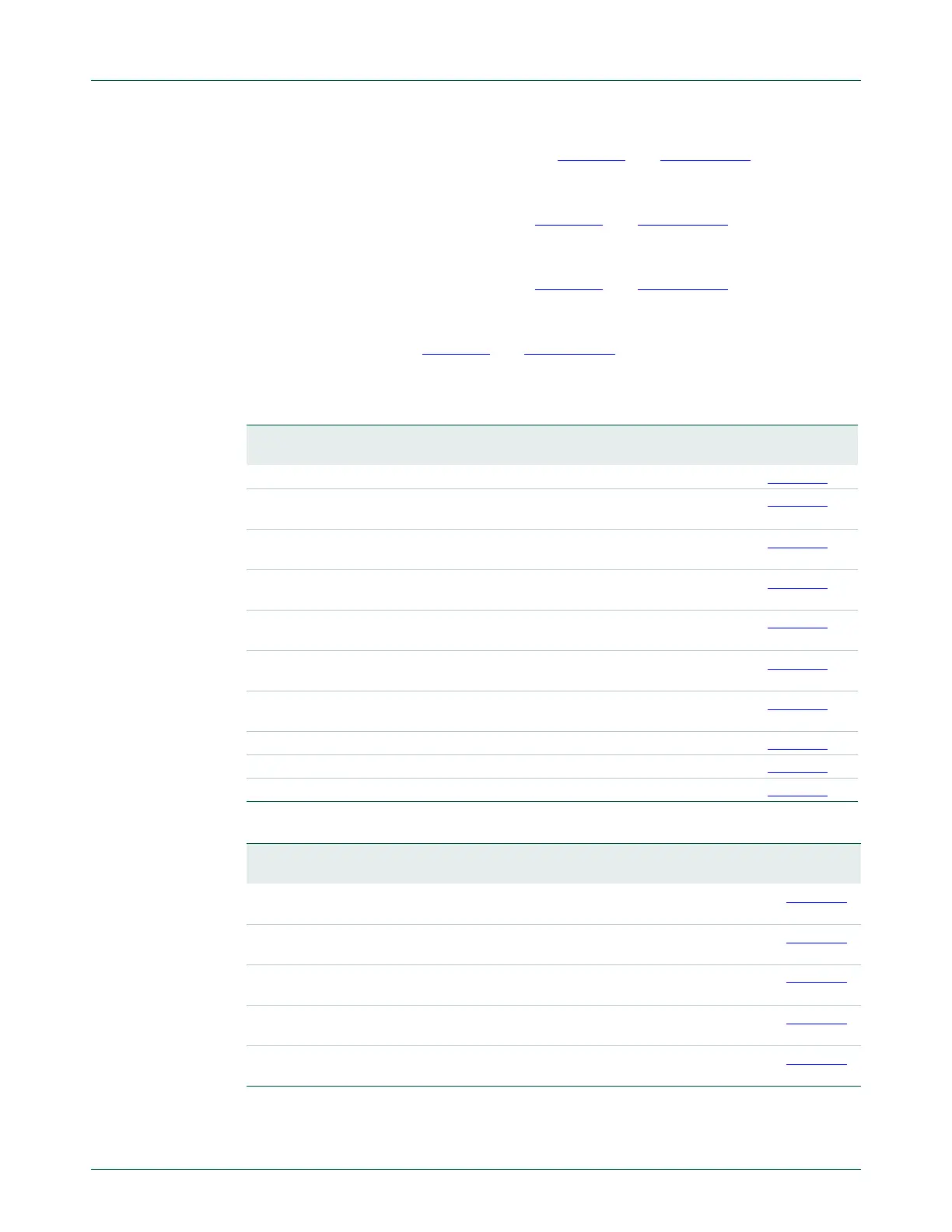

Table 138. Register overview: GPIO GROUP0 interrupt (base address 0x4005 C000)

Name Access Address

offset

Description Reset

value

Reference

CTRL R/W 0x000 GPIO grouped interrupt control

register

0 Table 151

PORT_POL0 R/W 0x020 GPIO grouped interrupt port 0 polarity

register

0xFFFF

FFFF

Table 152

PORT_POL1 R/W 0x024 GPIO grouped interrupt port 1 polarity

register

0xFFFF

FFFF

Table 153

PORT_ENA0 R/W 0x040 GPIO grouped interrupt port 0 enable

register

0 Table 154

PORT_ENA1 R/W 0x044 GPIO grouped interrupt port 1 enable

register

0 Table 155

Loading...

Loading...