UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 156 of 523

NXP Semiconductors

UM10462

Chapter 9: LPC11U3x/2x/1x GPIO

GPIO port addresses can be read and written as bytes, halfwords, or words.

[1] “ext” in this table and subsequent tables indicates that the data read after reset depends on the state of the pin, which in turn may

depend on an external source.

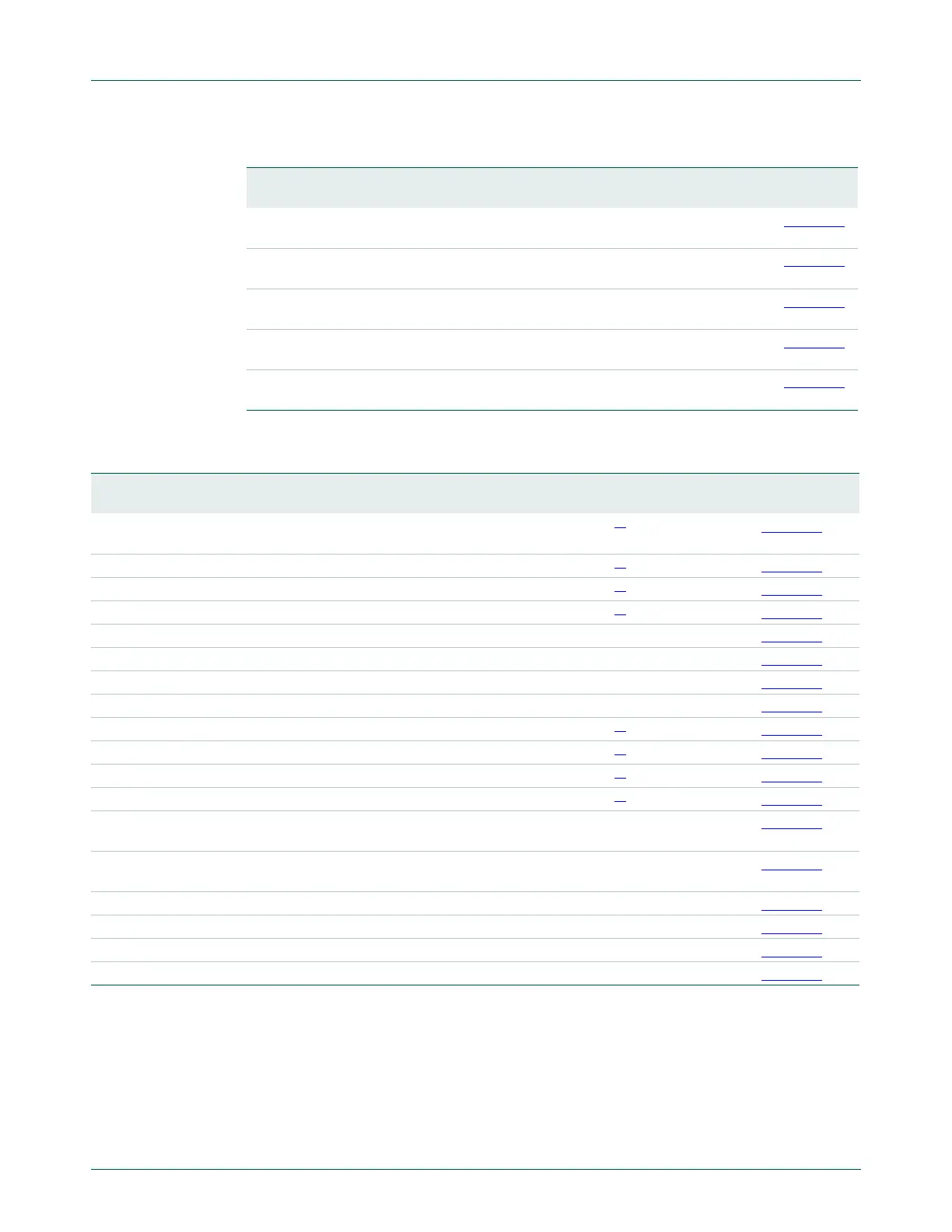

Table 139. Register overview: GPIO GROUP1 interrupt (base address 0x4006 0000)

Name Access Address

offset

Description Reset

value

Reference

CTRL R/W 0x000 GPIO grouped interrupt control

register

0 Table 151

PORT_POL0 R/W 0x020 GPIO grouped interrupt port 0 polarity

register

0xFFFF

FFFF

Table 152

PORT_POL1 R/W 0x024 GPIO grouped interrupt port 1 polarity

register

0xFFFF

FFFF

Table 153

PORT_ENA0 R/W 0x040 GPIO grouped interrupt port 0 enable

register

0 Table 154

PORT_ENA1 R/W 0x044 GPIO grouped interrupt port 1 enable

register

0 Table 155

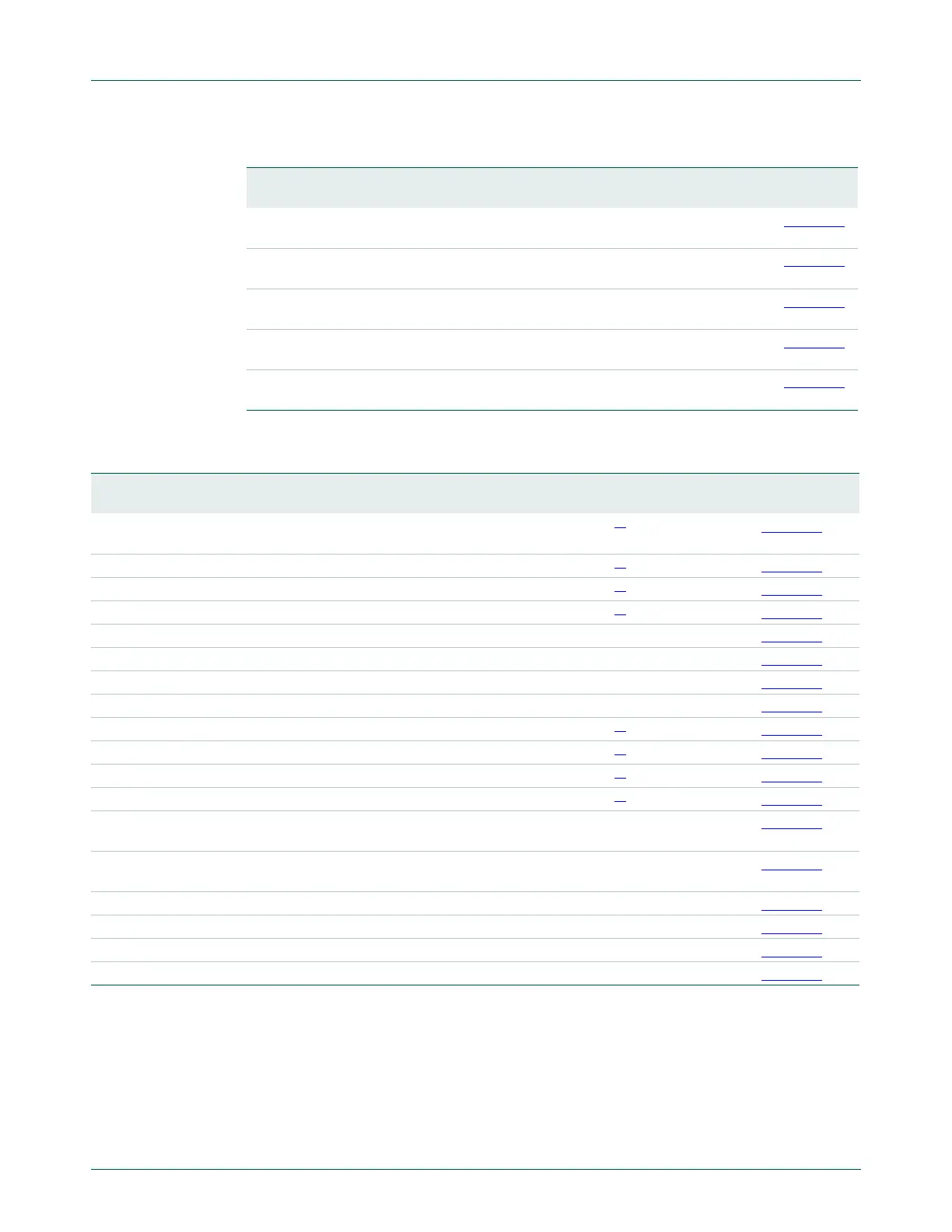

Table 140. Register overview: GPIO port (base address 0x5000 0000)

Name Access Address

offset

Description Reset

value

Width Reference

B0 to B23 R/W 0x0000 to 0x0018 Byte pin registers port 0; pins

PIO0_0 to PIO0_23

ext

[1]

byte (8 bit) Table 156

B32 to B63 R/W 0x0020 to 0x002F Byte pin registers port 1 ext

[1]

byte (8 bit) Table 157

W0 to W23 R/W 0x1000 to 0x1060 Word pin registers port 0 ext

[1]

word (32 bit) Table 158

W32 to W63 R/W 0x1080 to 0x10FC Word pin registers port 1 ext

[1]

word (32 bit) Table 159

DIR0 R/W 0x2000 Direction registers port 0 0 word (32 bit) Table 16 0

DIR1 R/W 0x2004 Direction registers port 1 0 word (32 bit) Table 161

MASK0 R/W 0x2080 Mask register port 0 0 word (32 bit) Table 162

MASK1 R/W 0x2084 Mask register port 1 0 word (32 bit) Table 163

PIN0 R/W 0x2100 Port pin register port 0 ext

[1]

word (32 bit) Table 164

PIN1 R/W 0x2104 Port pin register port 1 ext

[1]

word (32 bit) Table 165

MPIN0 R/W 0x2180 Masked port register port 0 ext

[1]

word (32 bit) Table 166

MPIN1 R/W 0x2184 Masked port register port 1 ext

[1]

word (32 bit) Table 167

SET0 R/W 0x2200 Write: Set register for port 0

Read: output bits for port 0

0 word (32 bit) Table 168

SET1 R/W 0x2204 Write: Set register for port 1

Read: output bits for port 1

0 word (32 bit) Table 169

CLR0 WO 0x2280 Clear port 0 NA word (32 bit) Table 170

CLR1 WO 0x2284 Clear port 1 NA word (32 bit) Table 171

NOT0 WO 0x2300 Toggle port 0 NA word (32 bit) Table 172

NOT1 WO 0x2304 Toggle port 1 NA word (32 bit) Table 173

Loading...

Loading...