UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 259 of 523

NXP Semiconductors

UM10462

Chapter 12: LPC11U3x/2x/1x USART

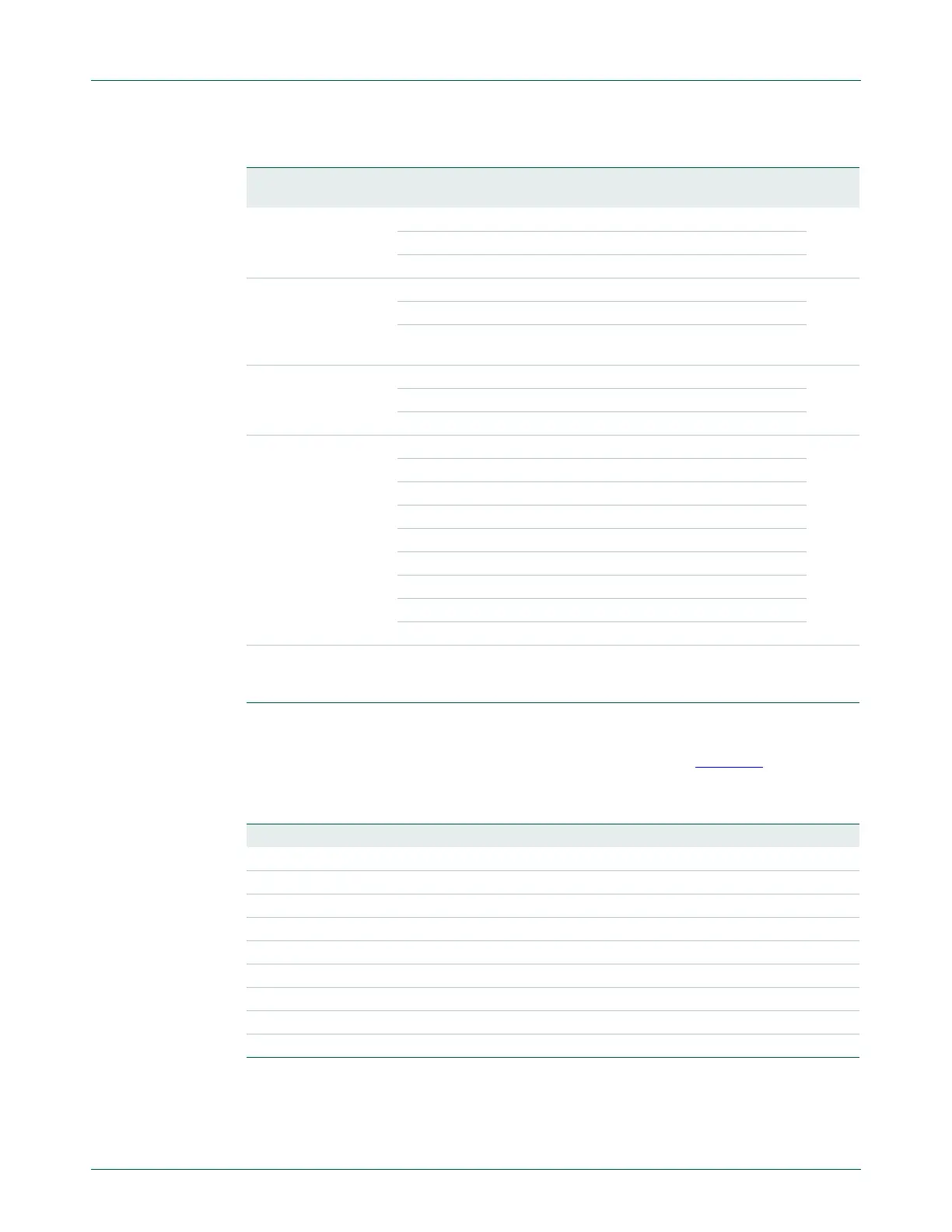

The PulseDiv bits in the ICR are used to select the pulse width when the fixed pulse width

mode is used in IrDA mode (IrDAEn = 1 and FixPulseEn = 1). The value of these bits

should be set so that the resulting pulse width is at least 1.63 µs. Table 246

shows the

possible pulse widths.

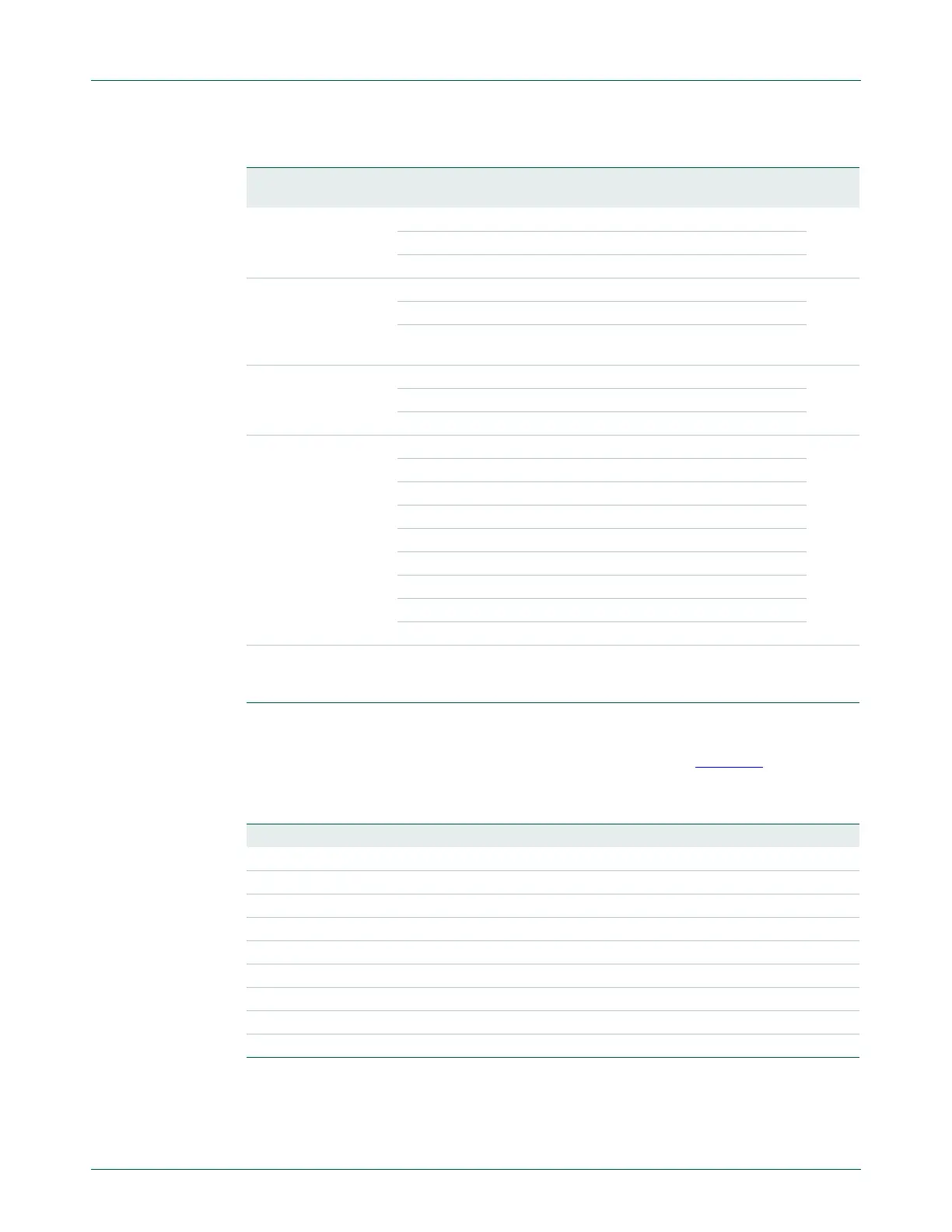

Table 245: IrDA Control Register (ICR - 0x4000 8024) bit description

Bit Symbol Value Description Reset

value

0 IRDAEN IrDA mode enable 0

0 IrDA mode is disabled.

1 IrDA mode is enabled.

1 IRDAINV Serial input inverter 0

0 The serial input is not inverted.

1 The serial input is inverted. This has no effect on the

serial output.

2 FIXPULSEEN IrDA fixed pulse width mode. 0

0 IrDA fixed pulse width mode disabled.

1 IrDA fixed pulse width mode enabled.

5:3 PULSEDIV Configures the pulse width when FixPulseEn = 1. 0

0x0 3 / (16 baud rate)

0x1 2 T

PCLK

0x2 4 T

PCLK

0x3 8 T

PCLK

0x4 16 T

PCLK

0x5 32 T

PCLK

0x6 64 T

PCLK

0x7 128 T

PCLK

31:6 - Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

0

Table 246: IrDA Pulse Width

FixPulseEn PulseDiv IrDA Transmitter Pulse width (µs)

0x3 / (16 baud rate)

102 T

PCLK

114 T

PCLK

128 T

PCLK

1316 T

PCLK

1432 T

PCLK

1564 T

PCLK

1 6 128 T

PCLK

1 7 256 T

PCLK

Loading...

Loading...