UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 418 of 523

NXP Semiconductors

UM10462

Chapter 20: LPC11U3x/2x/1x Flash programming firmware

20.16 Register description

20.16.1 EEPROM BIST start address register

The EEPROM BIST start address register is used to program the start address for the

BIST. During BIST the EEPROM devices are accessed with 16-bit read operations so the

LSB of the address is fixed zero.

20.16.2 EEPROM BIST stop address register

The EEPROM BIST stop address register is used to program the stop address for the

BIST and also to start the BIST. During BIST the EEPROM devices are accessed with

16-bit read operations so the LSB of the address is fixed zero.

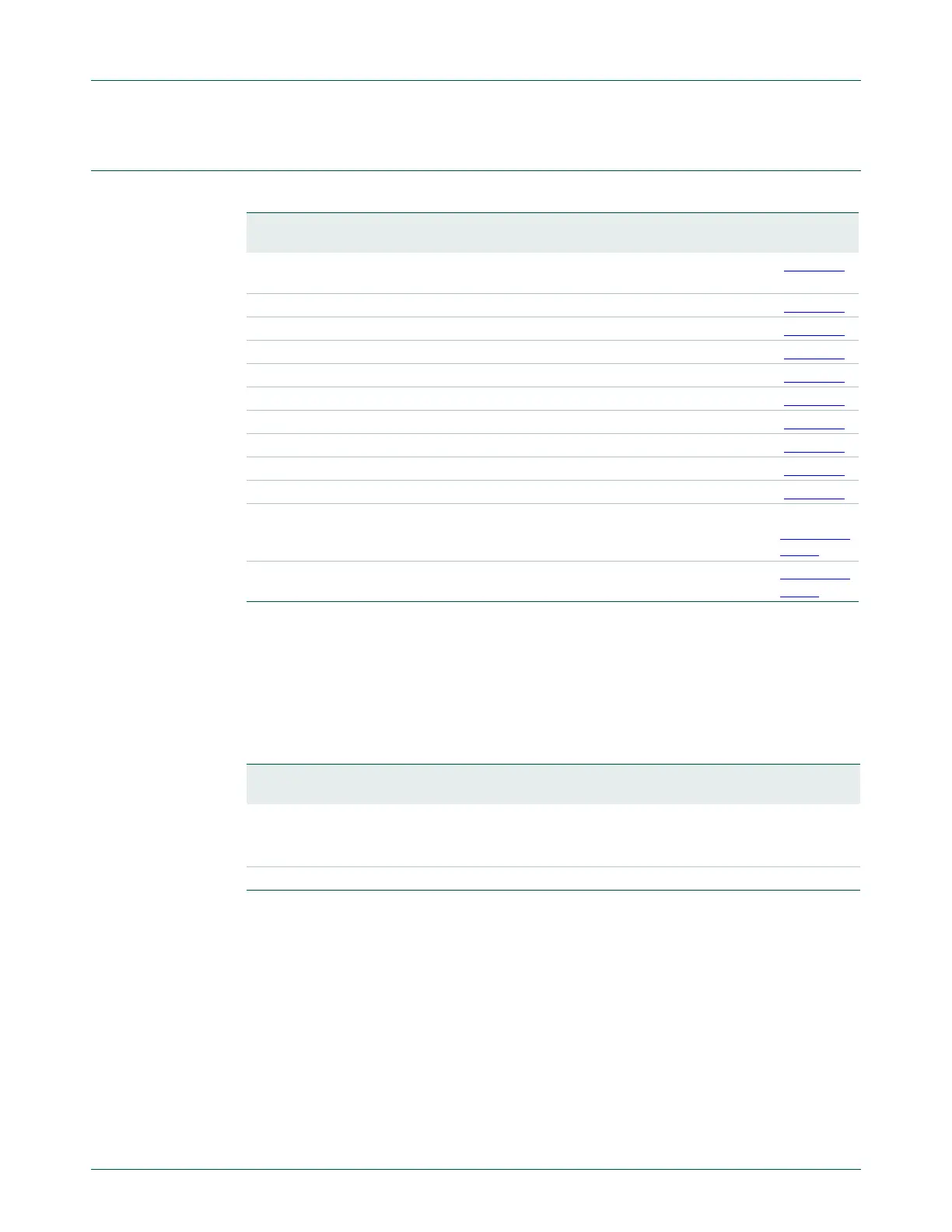

Table 397. Register overview: FMC (base address 0x4003 C000)

Name Access Address

offset

Description Reset

value

Reference

FLASHCFG R/W 0x010 Flash memory access time

configuration register

- Table 401

FMSSTART R/W 0x020 Signature start address register 0 Table 402

FMSSTOP R/W 0x024 Signature stop-address register 0 Table 403

FMSW0 R 0x02C Word 0 [31:0] - Table 404

FMSW1 R 0x030 Word 1 [63:32] - Table 405

FMSW2 R 0x034 Word 2 [95:64] - Table 406

FMSW3 R 0x038 Word 3 [127:96] - Table 407

EEMSSTART R/W 0x09C EEPROM BIST start address register 0x0 Table 398

EEMSSTOP R/W 0x0A0 EEPROM BIST stop address register 0x0 Table 399

EEMSSIG R 0x0A4 EEPROM 24-bit BIST signature register 0x0 Table 400

FMSTAT R 0xFE0 Signature generation status register 0

Section 20.

16.4.5

FMSTATCLR W 0xFE8 Signature generation status clear

register

- Section 20.

16.4.6

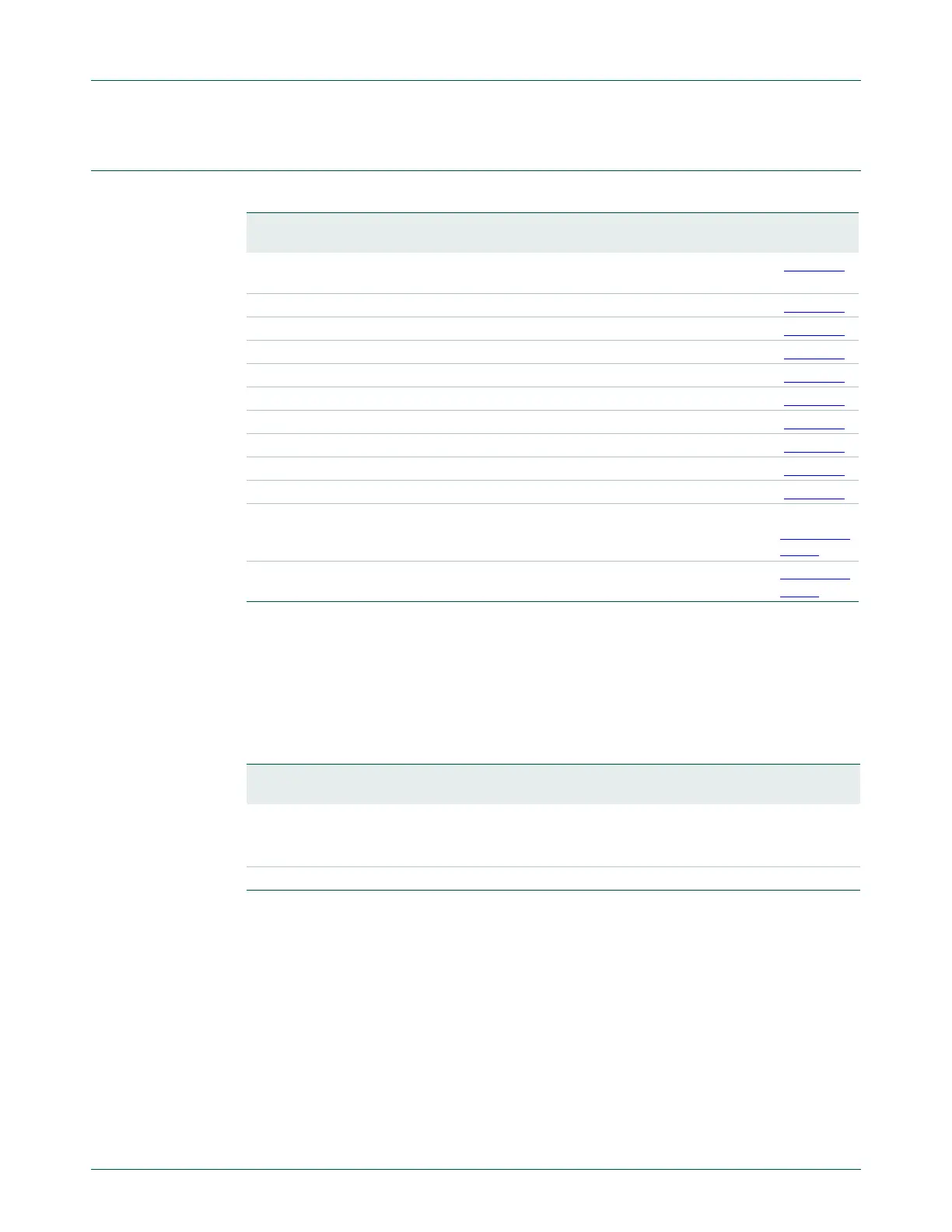

Table 398. EEPROM BIST start address register (EEMSSTART - address 0x4003 C09C) bit

description

Bit Symbol Description Reset

value

Access

13:0 STARTA BIST start address:

Bit 0 is fixed zero since only even addresses are

allowed.

0x0 R/W

31:14 - Reserved 0x0 -

Loading...

Loading...