UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 437 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

See the instruction descriptions Section 24–24.4.7.6 and Section 24–24.4.7.7 for more

information about how to access the program status registers.

Application Program Status Register: The APSR contains the current state of the

condition flags, from previous instruction executions. See the register summary in

Table 24–413

for its attributes. The bit assignments are:

See Section 24.4.4.1.4 for more information about the APSR negative, zero, carry or

borrow, and overflow flags.

Interrupt Program Status Register: The IPSR contains the exception number of the

current Interrupt Service Routine (ISR). See the register summary in Table 24–413

for

its attributes. The bit assignments are:

Execution Program Status Register: The EPSR contains the Thumb state bit.

See the register summary in Table 24–413

for the EPSR attributes. The bit assignments

are:

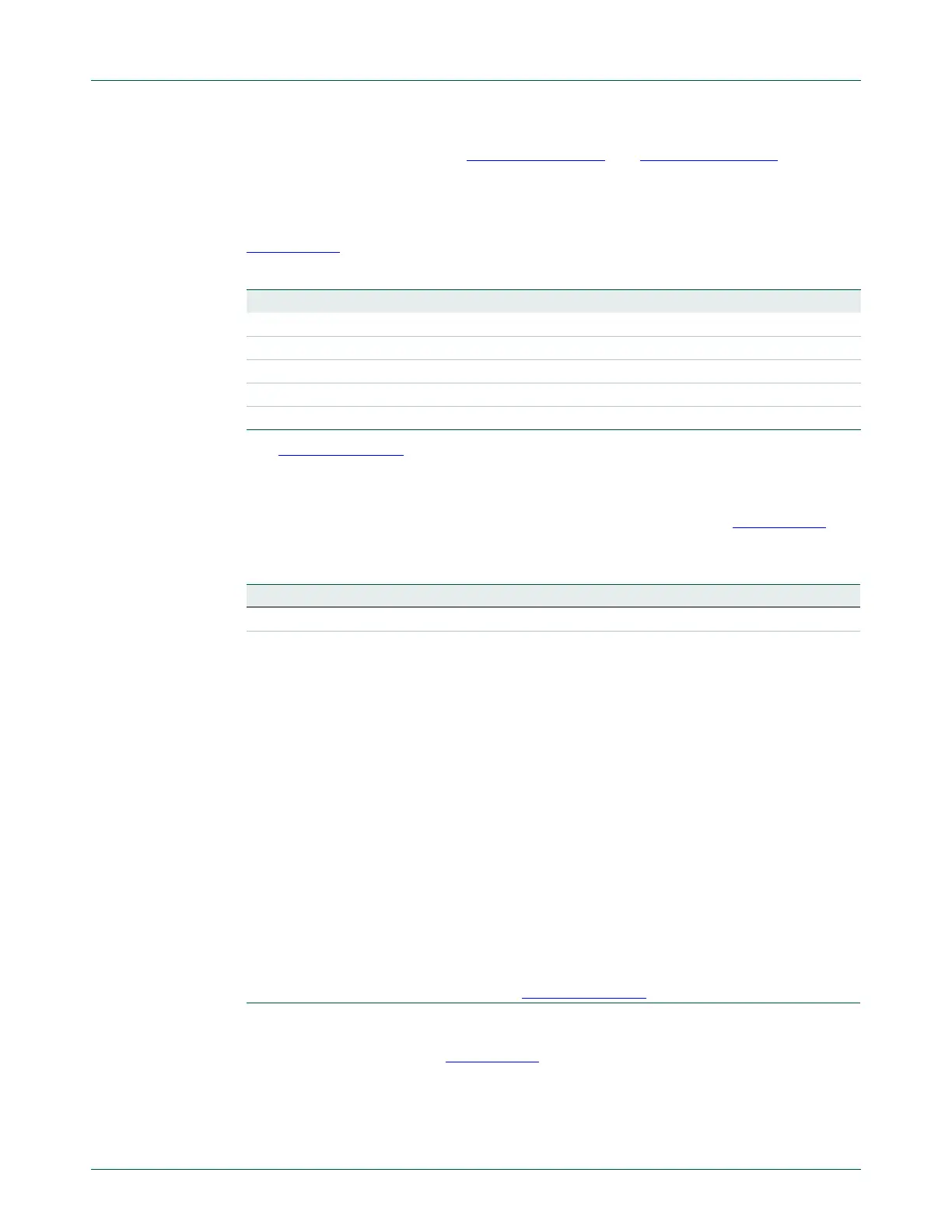

Table 415. APSR bit assignments

Bits Name Function

[31] N Negative flag

[30] Z Zero flag

[29] C Carry or borrow flag

[28] V Overflow flag

[27:0] - Reserved

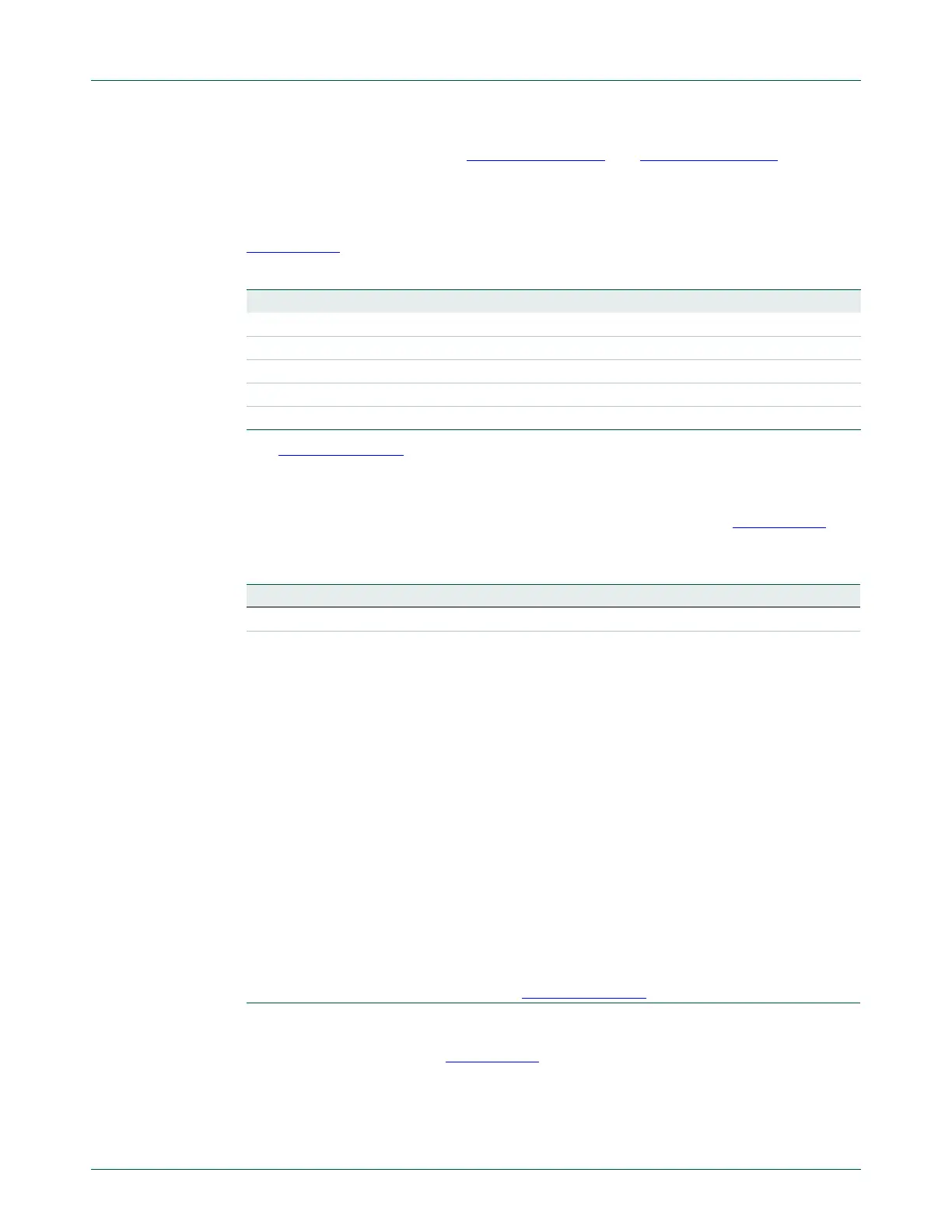

Table 416. IPSR bit assignments

Bits Name Function

[31:6] - Reserved

[5:0] Exception number This is the number of the current exception:

0 = Thread mode

1 = Reserved

2 = NMI

3 = HardFault

4-10 = Reserved

11 = SVCall

12, 13 = Reserved

14 = PendSV

15 = SysTick

16 = IRQ0

.

.

.

47 = IRQ31

48-63 = Reserved.

see Section 24–24.3.3.2

for more information.

Loading...

Loading...