UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 499 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

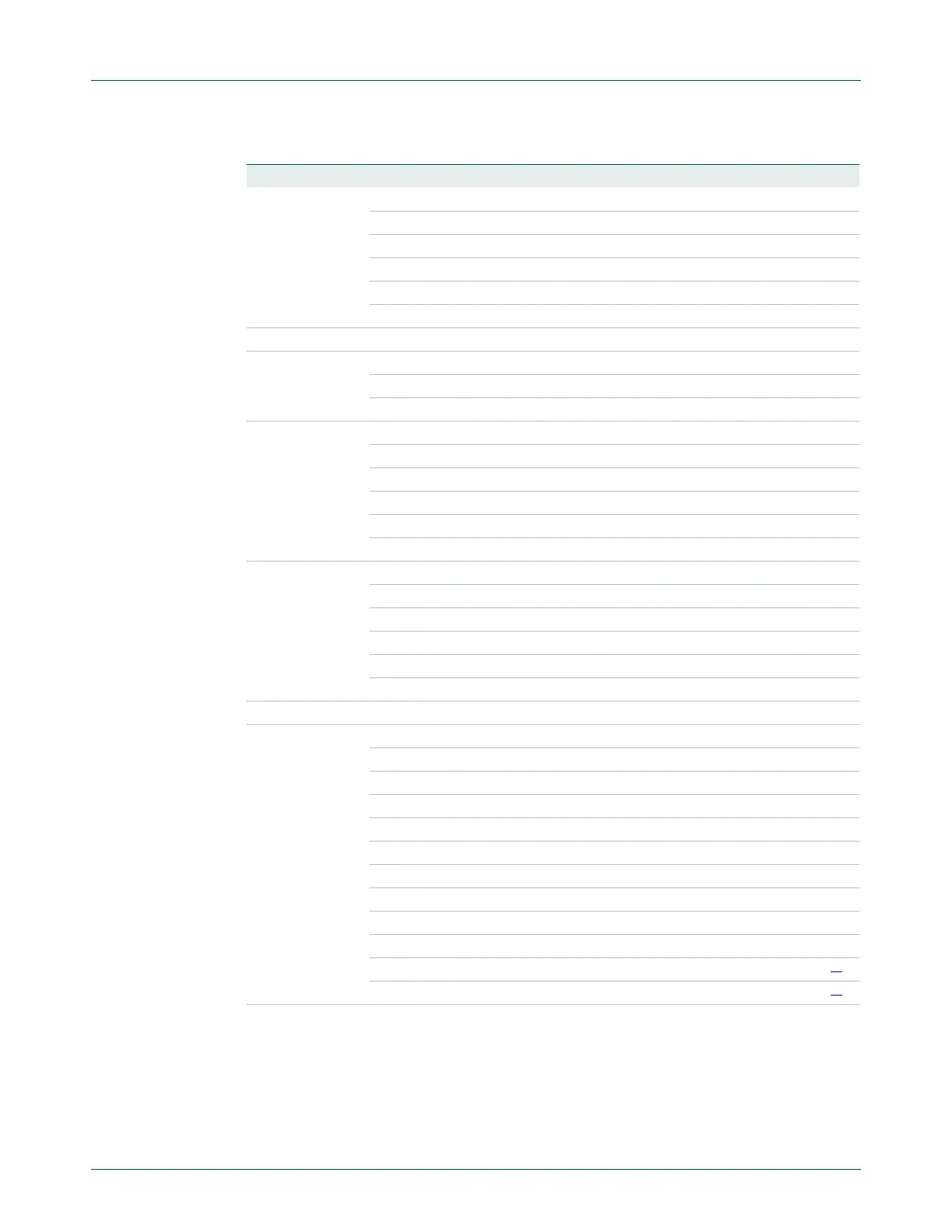

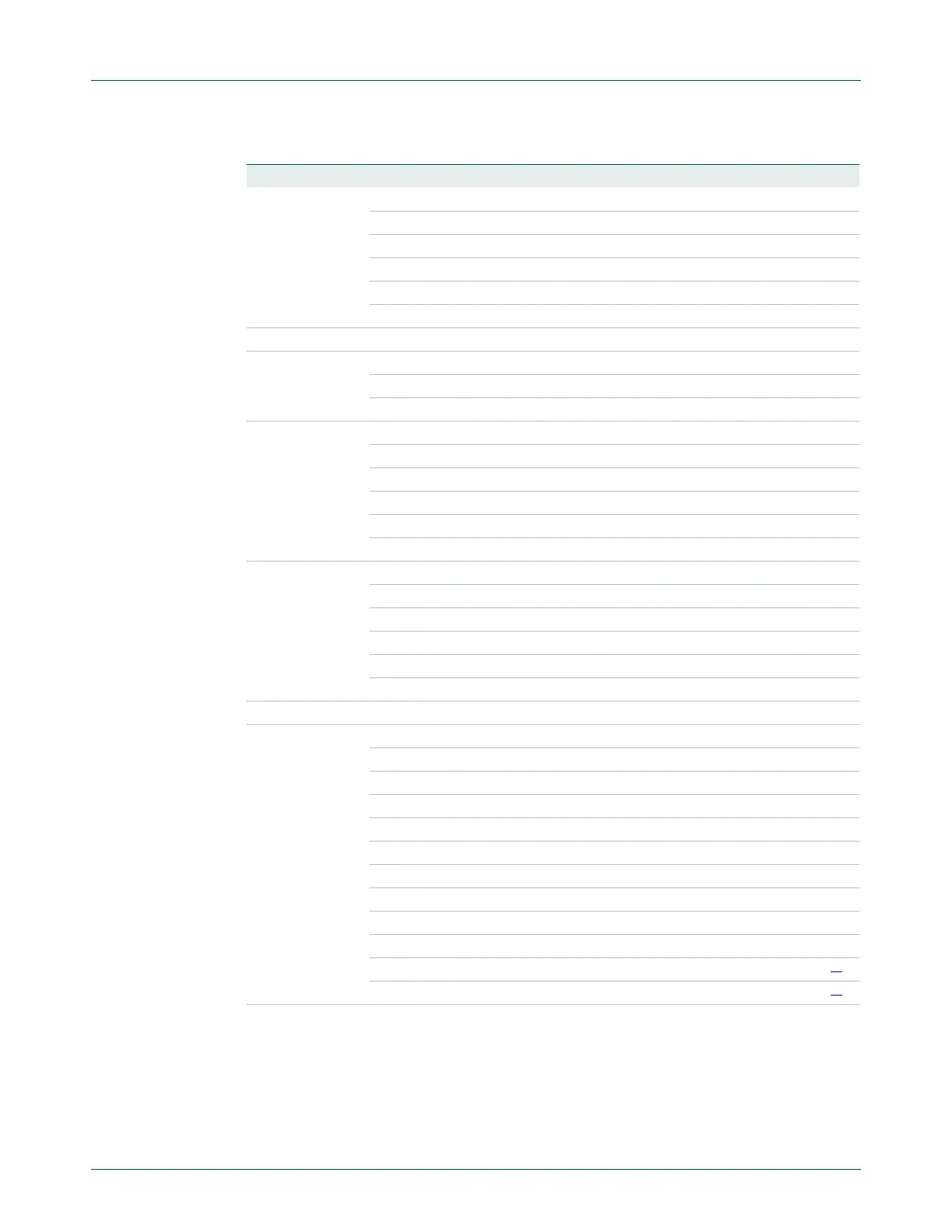

Subtract Lo and Lo SUBS Rd, Rn, Rm 1

3-bit immediate SUBS Rd, Rn, #<imm> 1

8-bit immediate SUBS Rd, Rd, #<imm> 1

With carry SBCS Rd, Rd, Rm 1

Immediate from SP SUB SP, SP, #<imm> 1

Negate RSBS Rd, Rn, #0 1

Multiply Multiply MULS Rd, Rm, Rd 1

Compare Compare CMP Rn, Rm 1

Negative CMN Rn, Rm 1

Immediate CMP Rn, #<imm> 1

Logical AND ANDS Rd, Rd, Rm 1

Exclusive OR EORS Rd, Rd, Rm 1

OR ORRS Rd, Rd, Rm 1

Bit clear BICS Rd, Rd, Rm 1

Move NOT MVNS Rd, Rm 1

AND test TST Rn, Rm 1

Shift Logical shift left by immediate LSLS Rd, Rm, #<shift> 1

Logical shift left by register LSLS Rd, Rd, Rs 1

Logical shift right by immediate LSRS Rd, Rm, #<shift> 1

Logical shift right by register LSRS Rd, Rd, Rs 1

Arithmetic shift right ASRS Rd, Rm, #<shift> 1

Arithmetic shift right by regist ASRS Rd, Rd, Rs 1

Rotate Rotate right by register RORS Rd, Rd, Rs 1

Load Word, immediate offset LDR Rd, [Rn, #<imm>] 2

Halfword, immediate offset LDRH Rd, [Rn, #<imm>] 2

Byte, immediate offset LDRB Rd, [Rn, #<imm>] 2

Word, register offset LDR Rd, [Rn, Rm] 2

Halfword, register offset LDRH Rd, [Rn, Rm] 2

Signed halfword, register offset LDRSH Rd, [Rn, Rm] 2

Byte, register offset LDRB Rd, [Rn, Rm] 2

Signed byte, register offset LDRSB Rd, [Rn, Rm] 2

PC-relative LDR Rd, <label> 2

SP-relative LDR Rd, [SP, #<imm>] 2

Multiple, excluding base LDM Rn!, {<loreglist>} 1 + N

[1]

Multiple, including base LDM Rn, {<loreglist>} 1 + N

[1]

Store Word, immediate offset STR Rd, [Rn, #<imm>] 2

Table 456. Cortex M0- instruction summary

Operation Description Assembler Cycles

Loading...

Loading...