UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 500 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

[1] N is the number of elements.

[2] N is the number of elements in the stack-pop list including PC and assumes load or store

does not generate a HardFault exception.

[3] 3 if taken, 1 if not taken.

[4] Cycle count depends on core and debug configuration.

[5] Excludes time spend waiting for an interrupt or event.

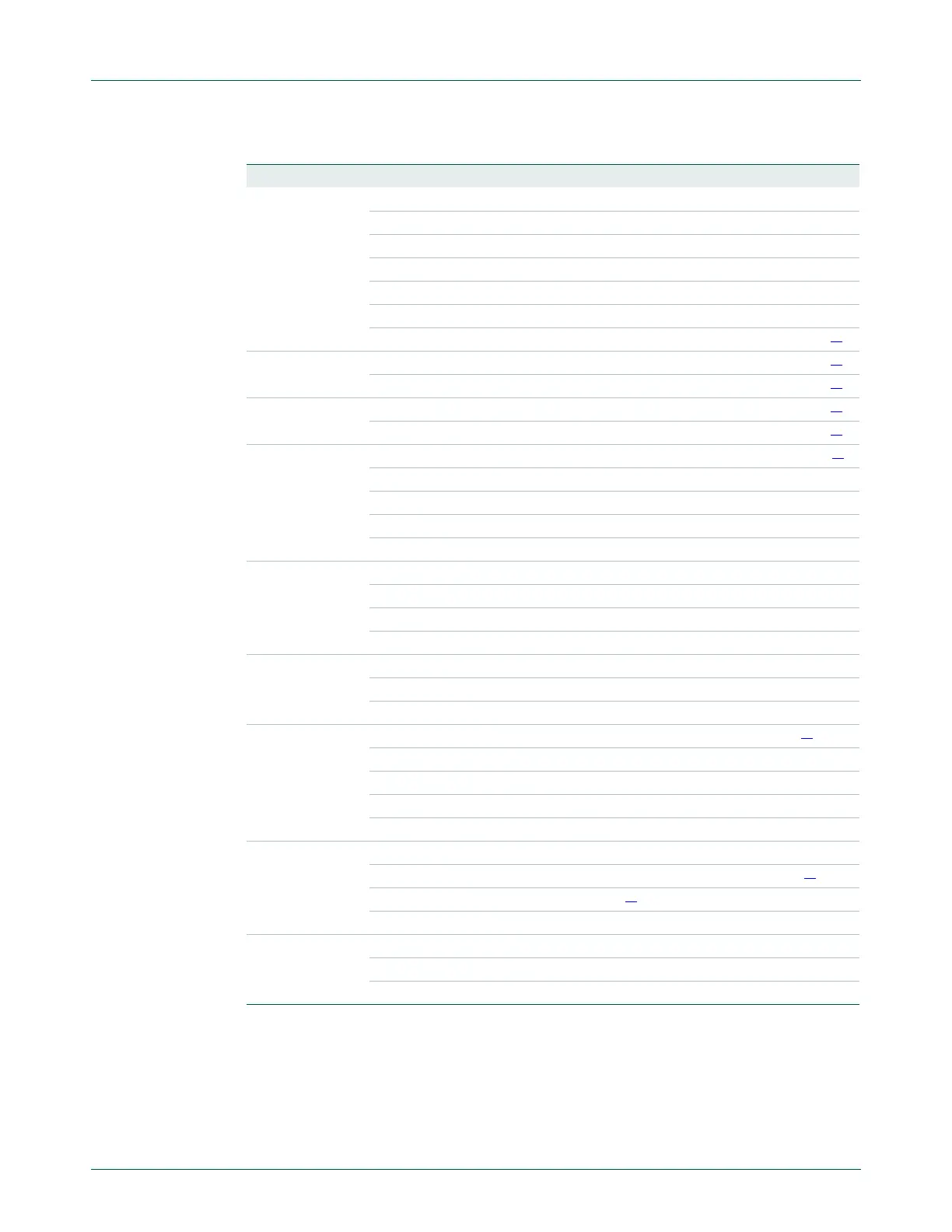

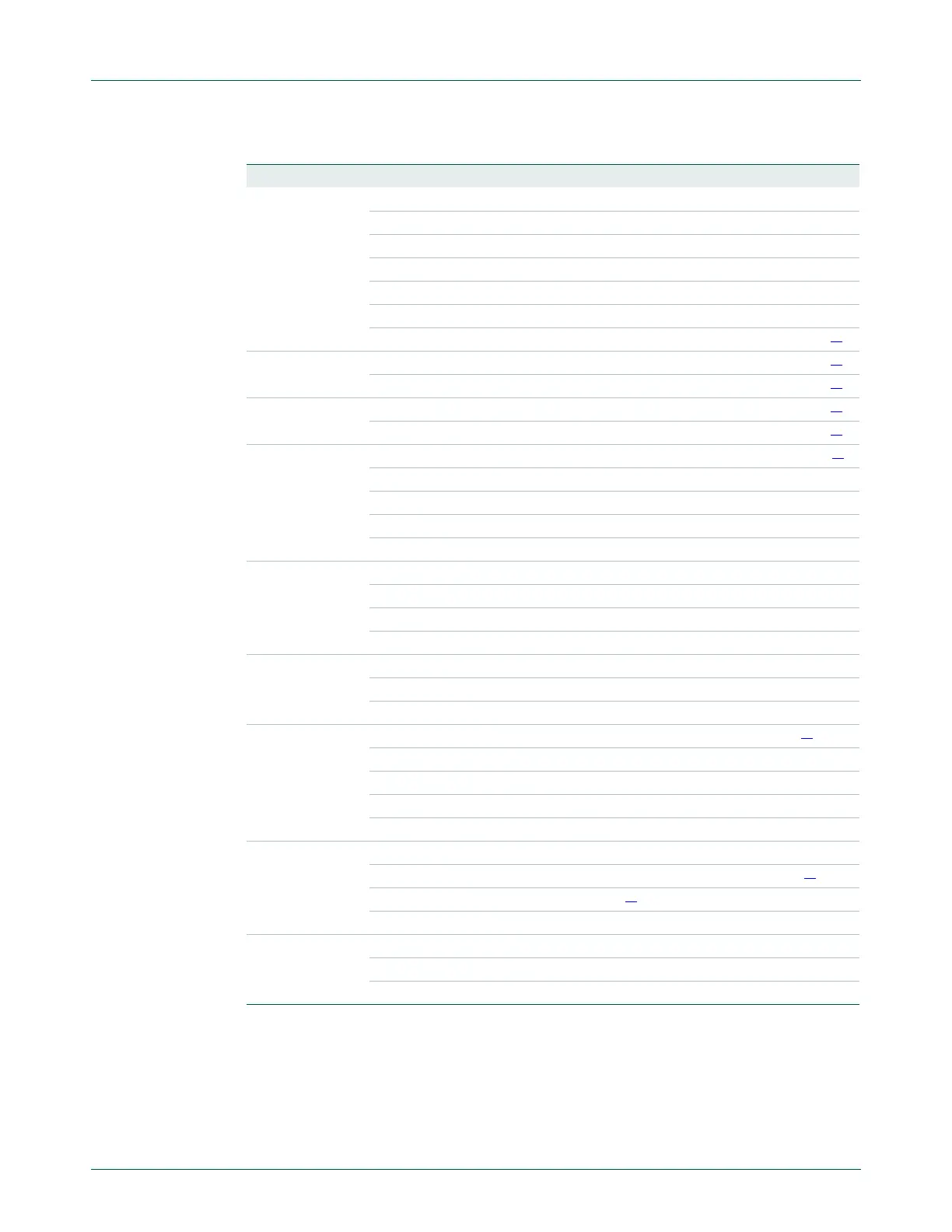

Store Halfword, immediate offset STRH Rd, [Rn, #<imm>] 2

Byte, immediate offset STRB Rd, [Rn, #<imm>] 2

Word, register offset STR Rd, [Rn, Rm] 2

Halfword, register offset STRH Rd, [Rn, Rm] 2

Byte, register offset STRB Rd, [Rn, Rm] 2

SP-relative STR Rd, [SP, #<imm>] 2

Multiple STM Rn!, {<loreglist>} 1 + N

[1]

Push Push PUSH {<loreglist>} 1 + N

[1]

Push with link register PUSH {<loreglist>, LR} 1 + N

[1]

Pop Pop POP {<loreglist>} 1 + N

[1]

Pop and return POP {<loreglist>, PC} 4 + N

[2]

Branch Conditional B<cc> <label> 1 or 3

[3]

Unconditional B <label> 3

With link BL <label> 4

With exchange BX Rm 3

With link and exchange BLX Rm 3

Extend Signed halfword to word SXTH Rd, Rm 1

Signed byte to word SXTB Rd, Rm 1

Unsigned halfword UXTH Rd, Rm 1

Unsigned byte UXTB Rd, Rm 1

Reverse Bytes in word REV Rd, Rm 1

Bytes in both halfwords REV16 Rd, Rm 1

Signed bottom half word REVSH Rd, Rm 1

State change Supervisor Call SVC <imm> -

[4]

Disable interrupts CPSID i 1

Enable interrupts CPSIE i 1

Read special register MRS Rd, <specreg> 4

Write special register MSR <specreg>, Rn 4

Hint Send event SEV 1

Wait for interrupt WFI 2

[5]

Yield YIELD

[6]

1

No operation NOP 1

Barriers Instruction synchronization ISB 4

Data memory DMB 4

Data synchronization DSB 4

Table 456. Cortex M0- instruction summary

Operation Description Assembler Cycles

Loading...

Loading...