Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 145

UG366 (v2.5) January 17, 2011

TX 8B/10B Encoder

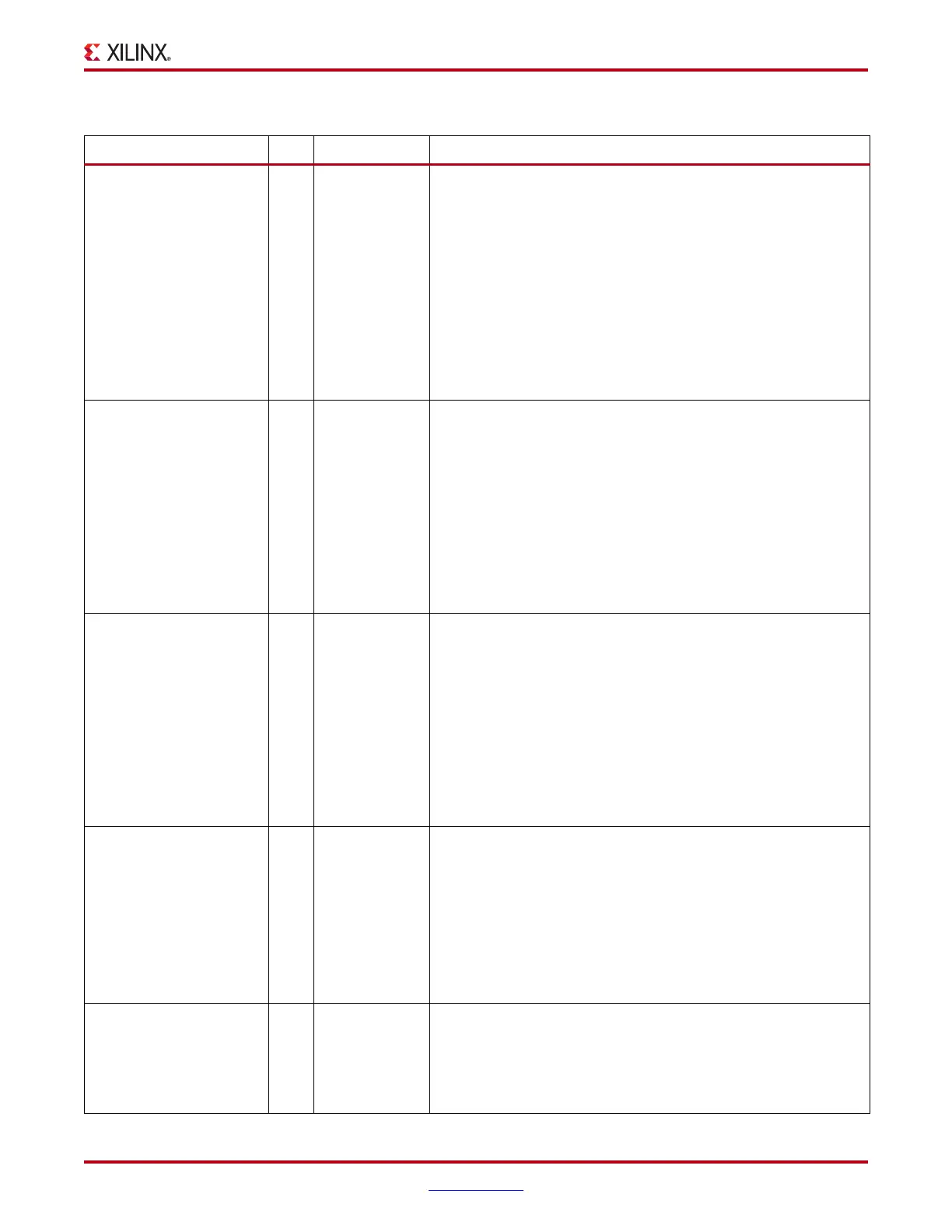

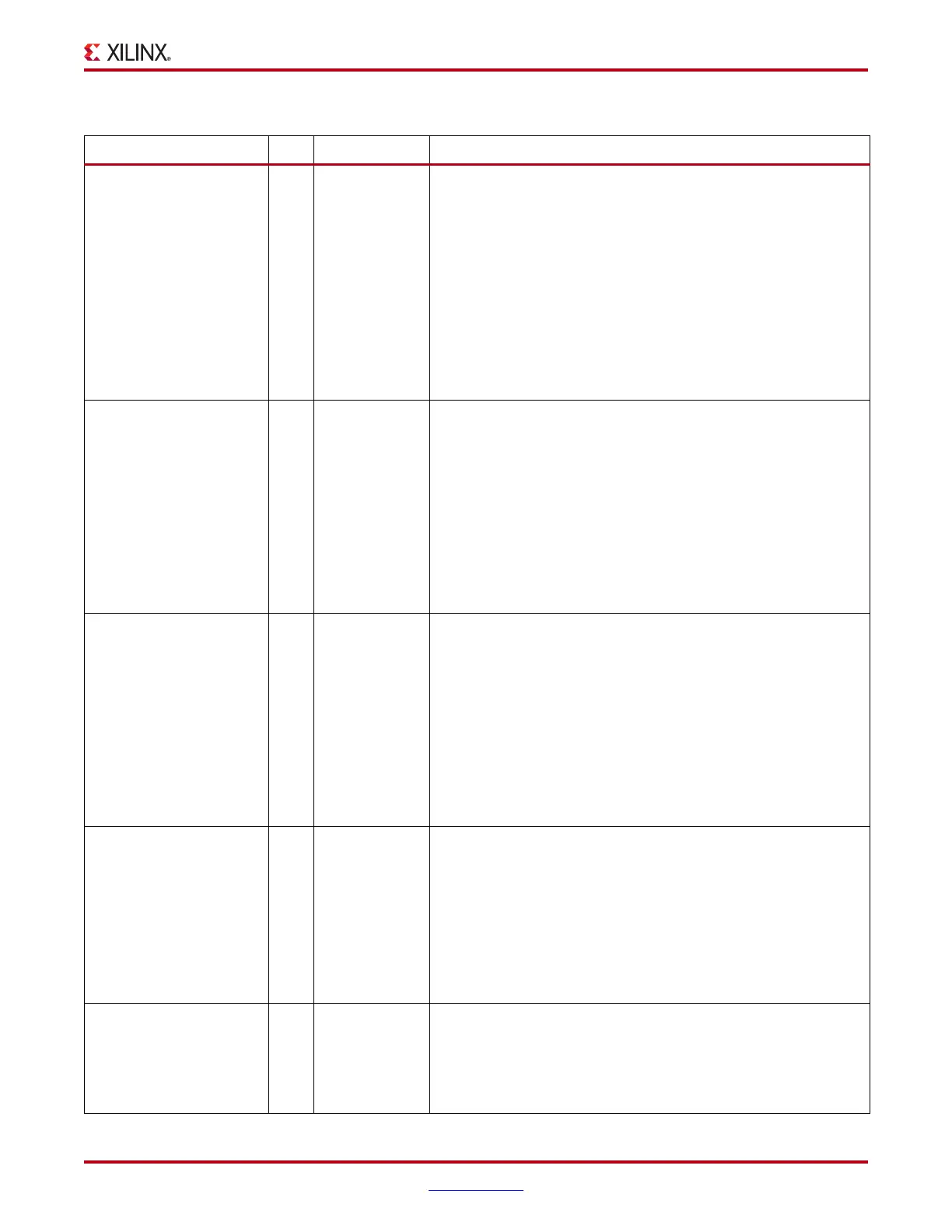

Table 3-12: TX Encoder Ports

Port Dir Clock Domain Description

TXBYPASS8B10B[3:0] In TXUSRCLK2 TXBYPASS8B10B controls the operation of the TX 8B/10B encoder

on a per-byte basis. It is only effective when TXENC8B10B is High

(8B/10B is enabled) and RX_DATA_WIDTH is {10, 20, 40}. See

Table 4-56, page 269 for additional information on

RX_DATA_WIDTH.

TXBYPASS8B10B[3] corresponds to TXDATA[31:24]

TXBYPASS8B10B[2] corresponds to TXDATA[23:16]

TXBYPASS8B10B[1] corresponds to TXDATA[15:8]

TXBYPASS8B10B[0] corresponds to TXDATA[7:0]

TXBYPASS8B10B[x] = 1, encoder for byte x is bypassed

TXBYPASS8B10B[x] = 0, encoder for byte x is used

TXCHARDISPMODE[3:0] In TXUSRCLK2 TXCHARDISPMODE and TXCHARDISPVAL allow the 8B/10B

disparity of outgoing data to be controlled when 8B/10B encoding

is enabled.

When 8B/10B encoding is disabled, TXCHARDISPMODE is used

to extend the data bus for TX interfaces with a width that is a

multiple of 10.

TXCHARDISPMODE[3] corresponds to TXDATA[31:24]

TXCHARDISPMODE[2] corresponds to TXDATA[23:16]

TXCHARDISPMODE[1] corresponds to TXDATA[15:8]

TXCHARDISPMODE[0] corresponds to TXDATA[7:0]

TXCHARDISPVAL[3:0] In TXUSRCLK2 TXCHARDISPVAL and TXCHARDISPMODE allow the 8B/10B

disparity of outgoing data disparity to be controlled when 8B/10B

encoding is enabled.

When 8B/10B encoding is disabled, TXCHARDISPVAL is used to

extend the data bus for 10- and 20-bit TX interfaces (see FPGA TX

Interface, page 128).

TXCHARDISPVAL[3] corresponds to TXDATA[31:24]

TXCHARDISPVAL[2] corresponds to TXDATA[23:16]

TXCHARDISPVAL[1] corresponds to TXDATA[15:8]

TXCHARDISPVAL[0] corresponds to TXDATA[7:0]

TXCHARISK[3:0] In TXUSRCLK2 TXCHARISK is set High to send TXDATA as an 8B/10B K

character. TXCHARISK should only be asserted for TXDATA

values representing valid K-characters.

TXCHARISK[3] corresponds to TXDATA[31:24]

TXCHARISK[2] corresponds to TXDATA[23:16]

TXCHARISK[1] corresponds to TXDATA[15:8]

TXCHARISK[0] corresponds to TXDATA[7:0]

TXCHARISK is undefined for bytes that bypass 8B/10B encoding.

TXENC8B10BUSE In TXUSRCLK2 TXENC8B10BUSE is set High to enable the 8B/10B encoder.

TX_DATA_WIDTH must be set to 10, 20, or 40 when the 8B/10B

encoder is enabled.

0: 8B/10B encoder bypassed. This option reduces latency.

1: 8B/10B encoder enabled.

Loading...

Loading...