196 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

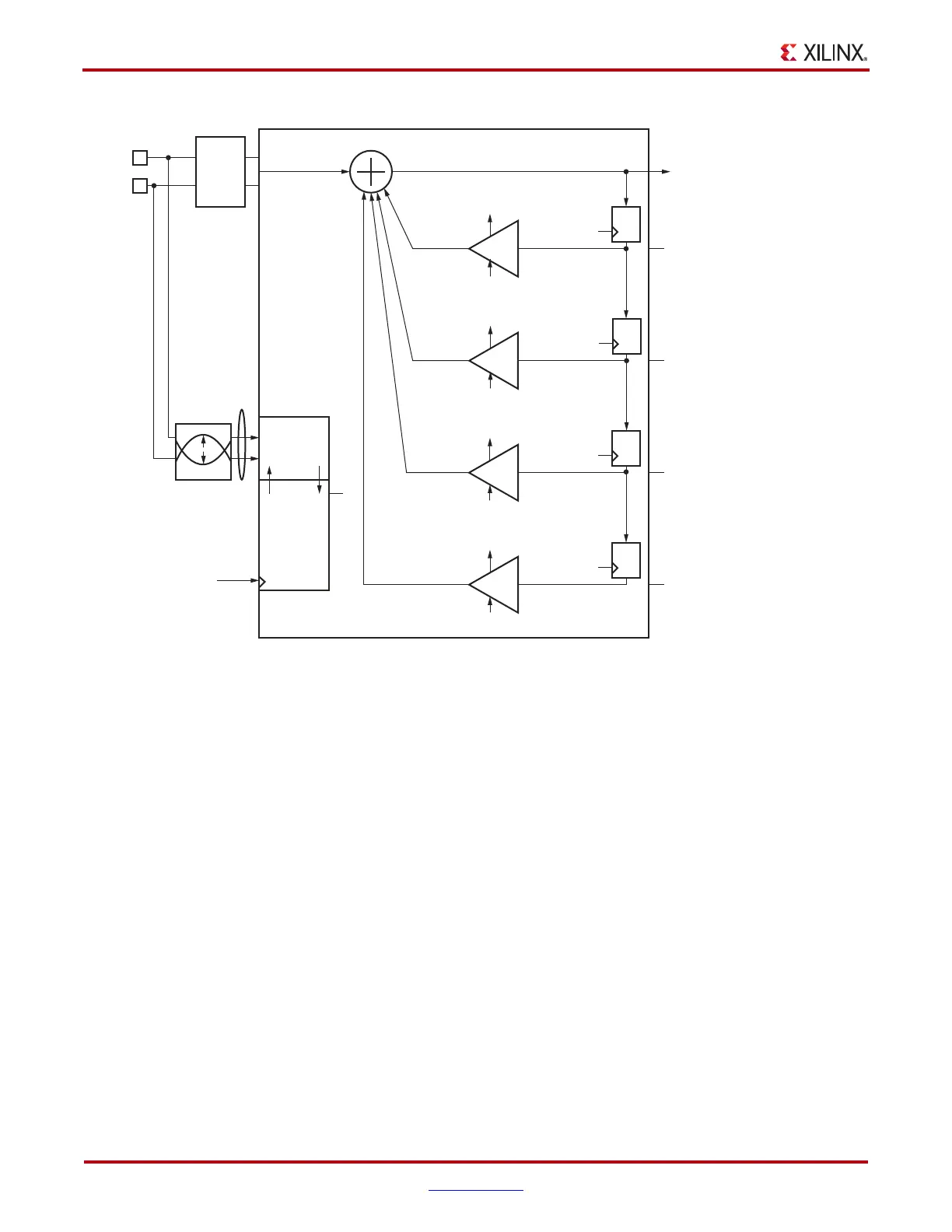

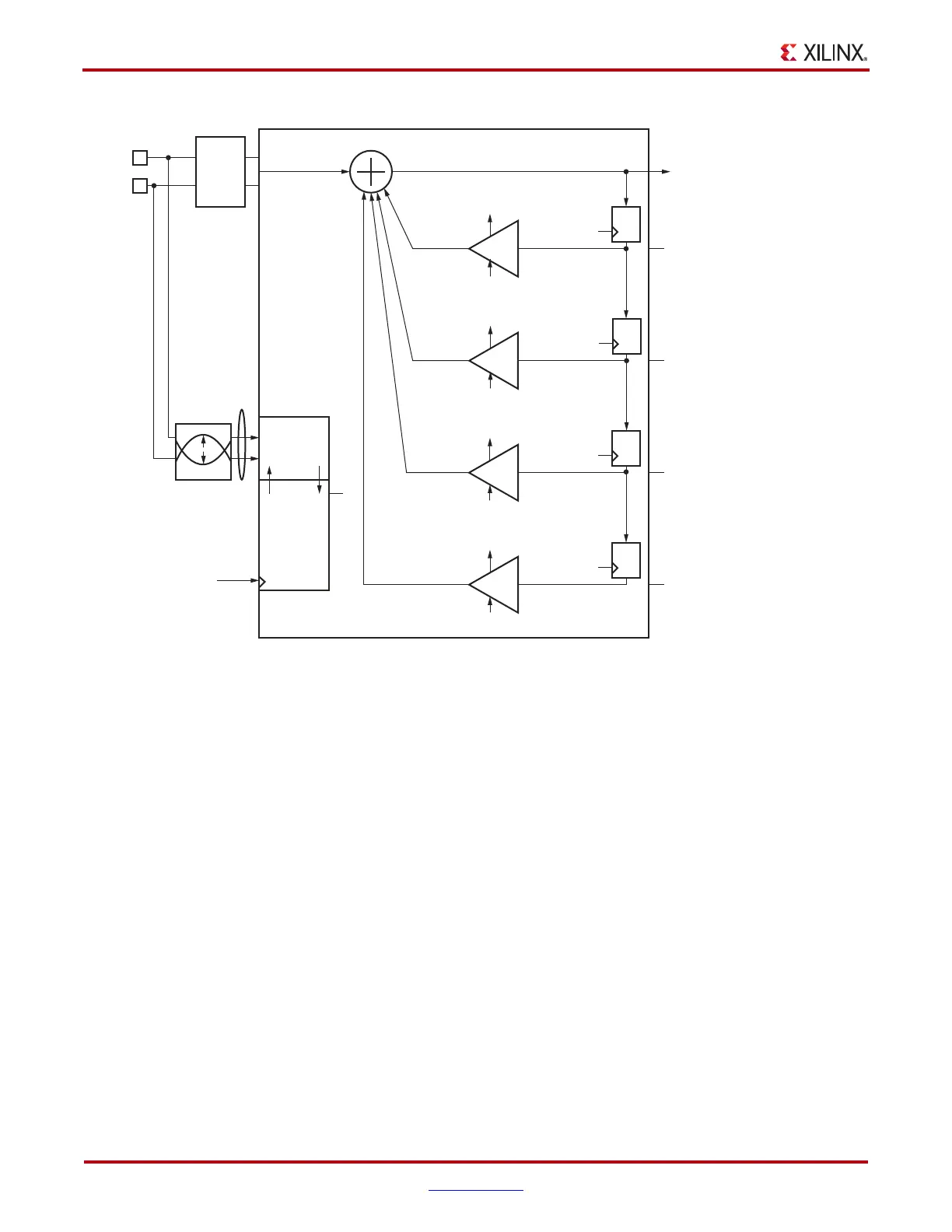

The DFE allows better compensation of transmission channel losses by providing a closer

adjustment of filter parameters than when using a linear equalizer. However, a DFE cannot

remove the pre-cursor of a transmitted bit. A linear equalizer allows pre-cursor and post-

cursor attenuation, but has only a coarse adaptor to the transmission channel

characteristic. The GTX DFE in the GTX RX is a discrete-time adaptive high-pass filter. The

TAP values of the DFE are the coefficients of this filter can be either set manually or by the

auto-calibration logic. The optimization criteria for the TAP values and the DFECLK delay

is the vertical eye opening. The DFETAPOVRD port switches off auto-calibration and

overrides the TAP values, and the DFEDLYOVRD port overrides the DFECLK delay.

X-Ref Target - Figure 4-12

Figure 4-12: DFE Conceptual View

UG366_c4_11_051509

Limiter

Automatic

TA P

Value

Control

DFE

Controller

DFE

DFE_CFG[9:0]

RX Serial Clock

–TAP1

DFE CLK

DFETAP1MONITOR[4:0]

DFETAP1[4:0]

DFECLK

T

–TAP2

DFETAP2MONITOR[4:0]

DFETAP2[4:0]

DFECLK

T

–TAP3

DFETAP3MONITOR[3:0]

DFETAP3[3:0]

DFECLK

T

–TAP4

DFETAP4MONITOR[3:0]

DFETAP1MONITOR[4:0]

DFETAP2MONITOR[4:0]

DFETAP3MONITOR[3:0]

DFETAP4MONITOR[3:0]

DFETAP4[3:0]

DFECLK

T

P

N

To CDR

DFEEYEDACMONITOR[4:0]

Loading...

Loading...