242 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

Table 4-47 defines the RX clock correction attributes.

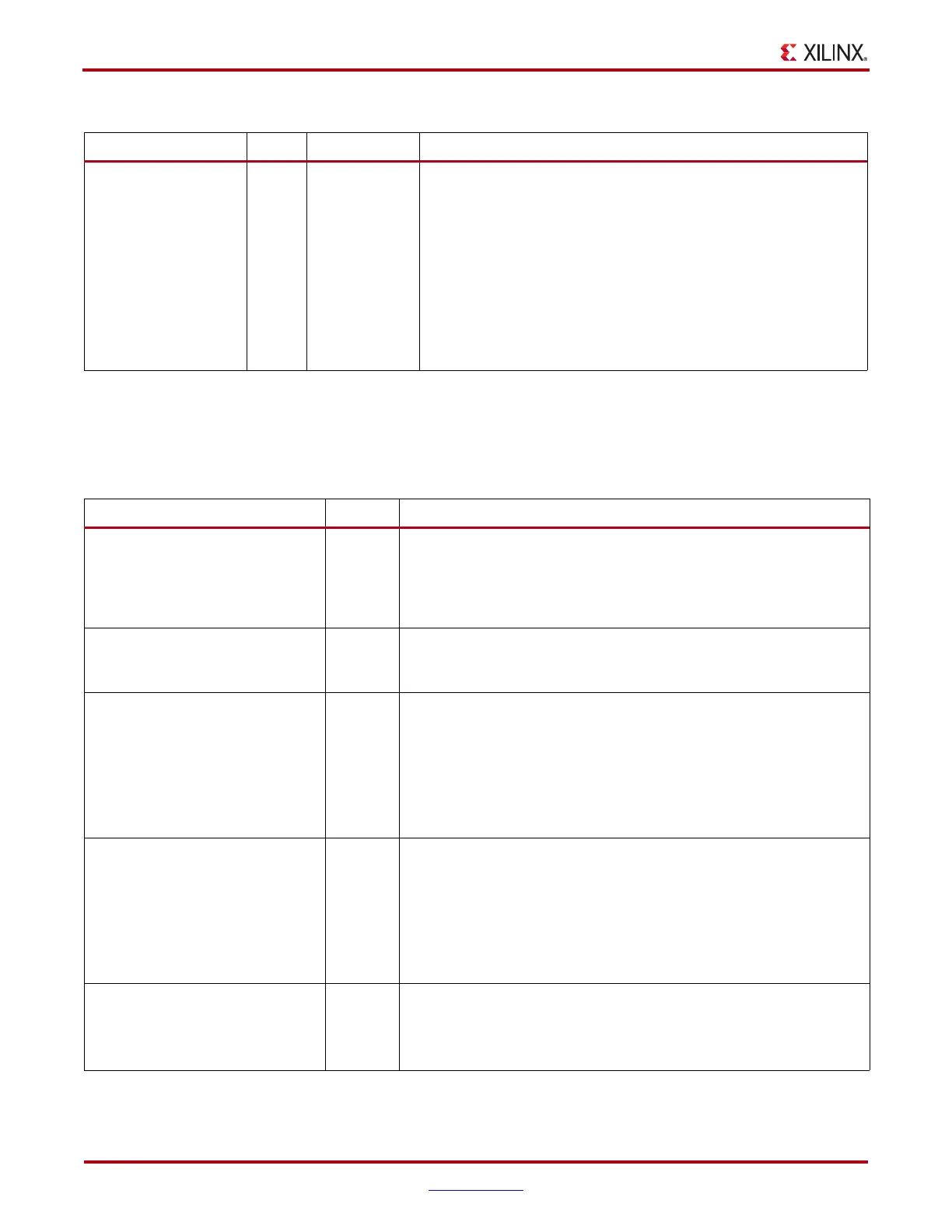

RXCLKCORCNT[2:0] Out RXUSRCLK2 Reports the clock correction status of the RX elastic buffer:

000: No clock correction

001: 1 sequence skipped

010: 2 sequences skipped

011: 3 sequences skipped

100: 4 sequences skipped

101: Reserved

110: 2 sequences added

111: 1 sequence added

Notes:

1. If an RX elastic buffer overflow or an RX elastic buffer underflow condition occurs, the content of the RX elastic buffer becomes

invalid, and the RX elastic buffer needs re-initialization by asserting/deasserting RXBUFRESET.

Table 4-46: RX Clock Correction Ports (Cont’d)

Port Dir Clock Domain Description

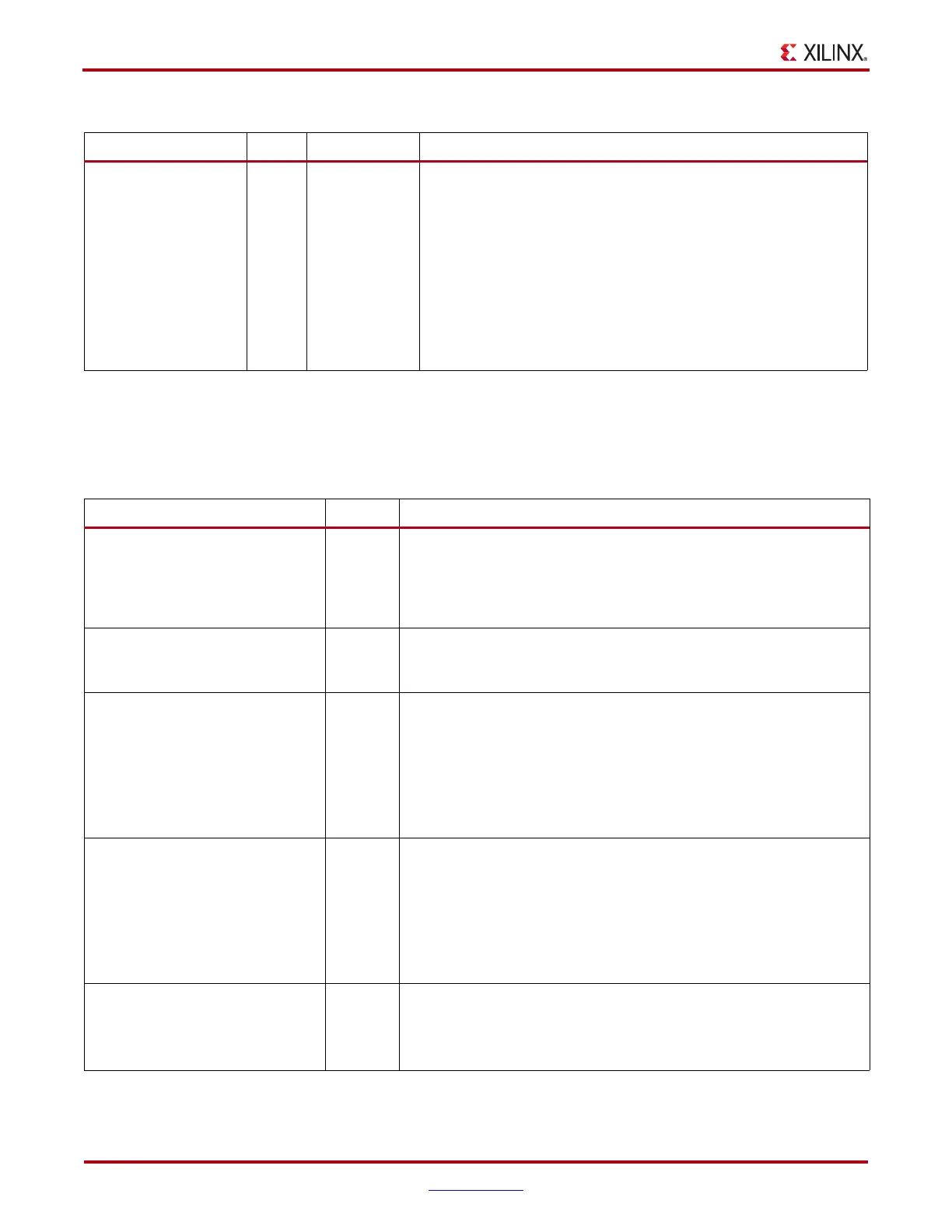

Table 4-47: RX Clock Correction Attributes

Attribute Type Description

CLK_COR_ADJ_LEN Integer This attribute defines the size of the adjustment (number of bytes

repeated or skipped) in a clock correction. The bytes skipped or

repeated always start from the beginning of the clock correction

sequence to allow more bytes to be replaced than in the specified clock

correction sequence. Valid lengths are 1, 2, and 4 bytes.

CLK_COR_DET_LEN Integer This attribute defines the length of the sequence that the transceiver

matches to detect opportunities for clock correction. Valid lengths are

1, 2, and 4 bytes.

CLK_COR_INSERT_IDLE_FLAG Boolean Controls whether the RXRUNDISP input status indicates running

disparity or inserted-idle (clock correction sequence) flag.

FALSE: RXRUNDISP indicates running disparity when RXDATA is

decoded data.

TRUE: RXRUNDISP is raised for the first byte of each inserted

(repeated) clock correction (“Idle”) sequence (when RXDATA is

decoded data).

CLK_COR_KEEP_IDLE Boolean Controls whether the RX elastic buffer must retain at least one clock

correction sequence in the byte stream.

FALSE: The transceiver can remove all clock correction sequences to

further re-center the RX elastic buffer during clock correction.

TRUE: In the final RXDATA stream, the transceiver must leave at

least one clock correction sequence per continuous stream of clock

correction sequences.

CLK_COR_MAX_LAT Integer Specifies the maximum RX elastic buffer latency. If the RX elastic buffer

exceeds CLK_COR_MAX_LAT, the clock correction circuit removes

incoming clock correction sequences to prevent overflow.

Valid values for this attribute range from 3 to 48.

Loading...

Loading...