Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 305

UG366 (v2.5) January 17, 2011

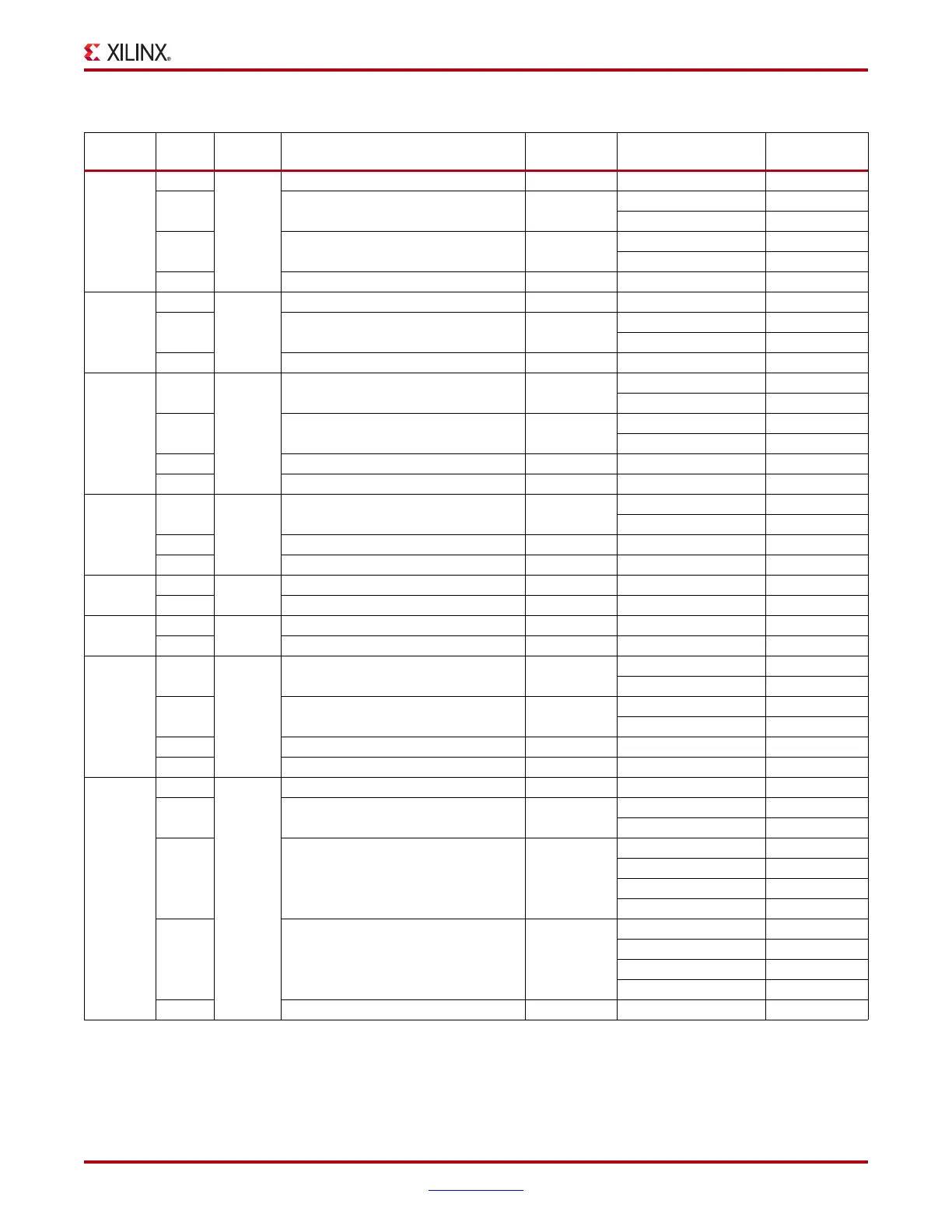

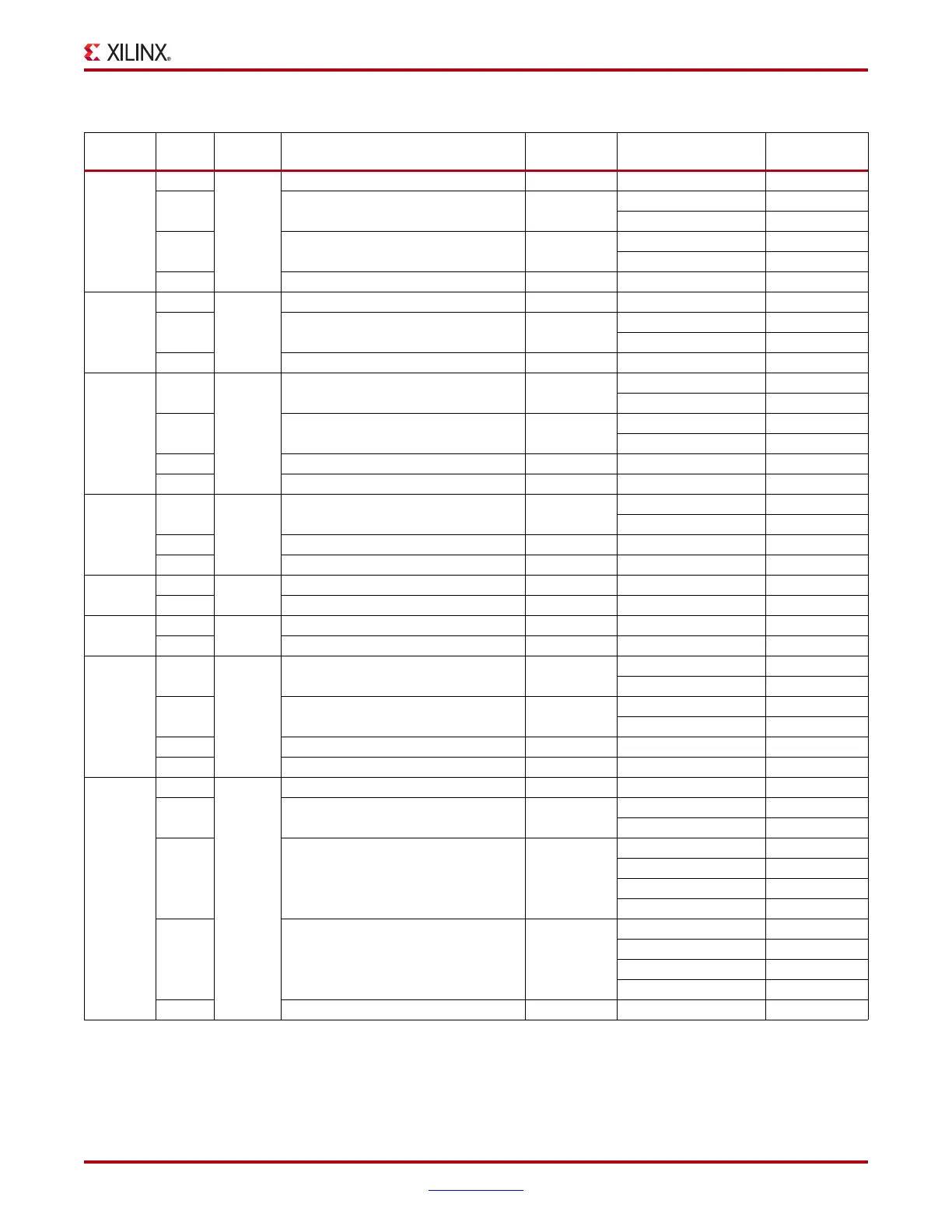

Bh

15:12

R/W

RX_IDLE_HI_CNT 3:0 0-15

1

(1)

11 RX_XCLK_SEL

RXREC

0

RXUSR 1

10 RX_EN_IDLE_RESET_BUF

FALSE

0

TRUE 1

9:0 CHAN_BOND_SEQ_2_4 9:0 0-1023 1

(1)

Ch

15:14

R/W

Reserved 1:0

13 RX_FIFO_ADDR_MODE

FALSE

0

TRUE 1

12:0 Reserved 12:0

Dh

15

R/W

CLK_COR_PRECEDENCE

FALSE

0

TRUE 1

14 CLK_CORRECT_USE

FALSE

0

TRUE 1

13:10 CLK_COR_SEQ_1_ENABLE 3:0 0-15 1

(1)

9:0 CLK_COR_SEQ_1_1 9:0 0-1023 1

(1)

Eh

15

R/W

CLK_COR_KEEP_IDLE

FALSE

0

TRUE 1

14:10 CLK_COR_REPEAT_WAIT 4:0 0-31 1

(1)

9:0 CLK_COR_SEQ_1_2 9:0 0-1023 1

(1)

Fh

15:10

R/W

CLK_COR_MIN_LAT 5:0 3-48

1

(1)

9:0 CLK_COR_SEQ_1_3 9:0 0-1023 1

(1)

10h

15:10

R/W

CLK_COR_MAX_LAT 5:0 3-48

1

(1)

9:0 CLK_COR_SEQ_1_4 9:0 0-1023 1

(1)

11h

15

R/W

CLK_COR_INSERT_IDLE_FLAG

FALSE

0

TRUE 1

14 CLK_COR_SEQ_2_USE

FALSE

0

TRUE 1

13:10 CLK_COR_SEQ_2_ENABLE 3:0 0-15 1

(1)

9:0 CLK_COR_SEQ_2_1 9:0 0-1023 1

(1)

12h

15

R/W

Reserved

14 SHOW_REALIGN_COMMA

FALSE

0

TRUE 1

13:12 RX_SLIDE_MODE 1:0

OFF

00

AUTO 01

PCS 10

PMA 11

11:10 CLK_COR_ADJ_LEN 1:0

1

00

2 01

Reserved

4

11

9:0 CLK_COR_SEQ_2_2 9:0 0-1023 1

(1)

Table B-1: Attributes DRP Address Map (Cont’d)

DADDR

DRP Bits R/W Attribute Name Attribute Bits Attribute Encoding

DRP Binary

Encoding

Loading...

Loading...