UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 336 of 523

NXP Semiconductors

UM10462

Chapter 15: LPC11U3x/2x/1x 16-bit counter/timers CT16B0/1

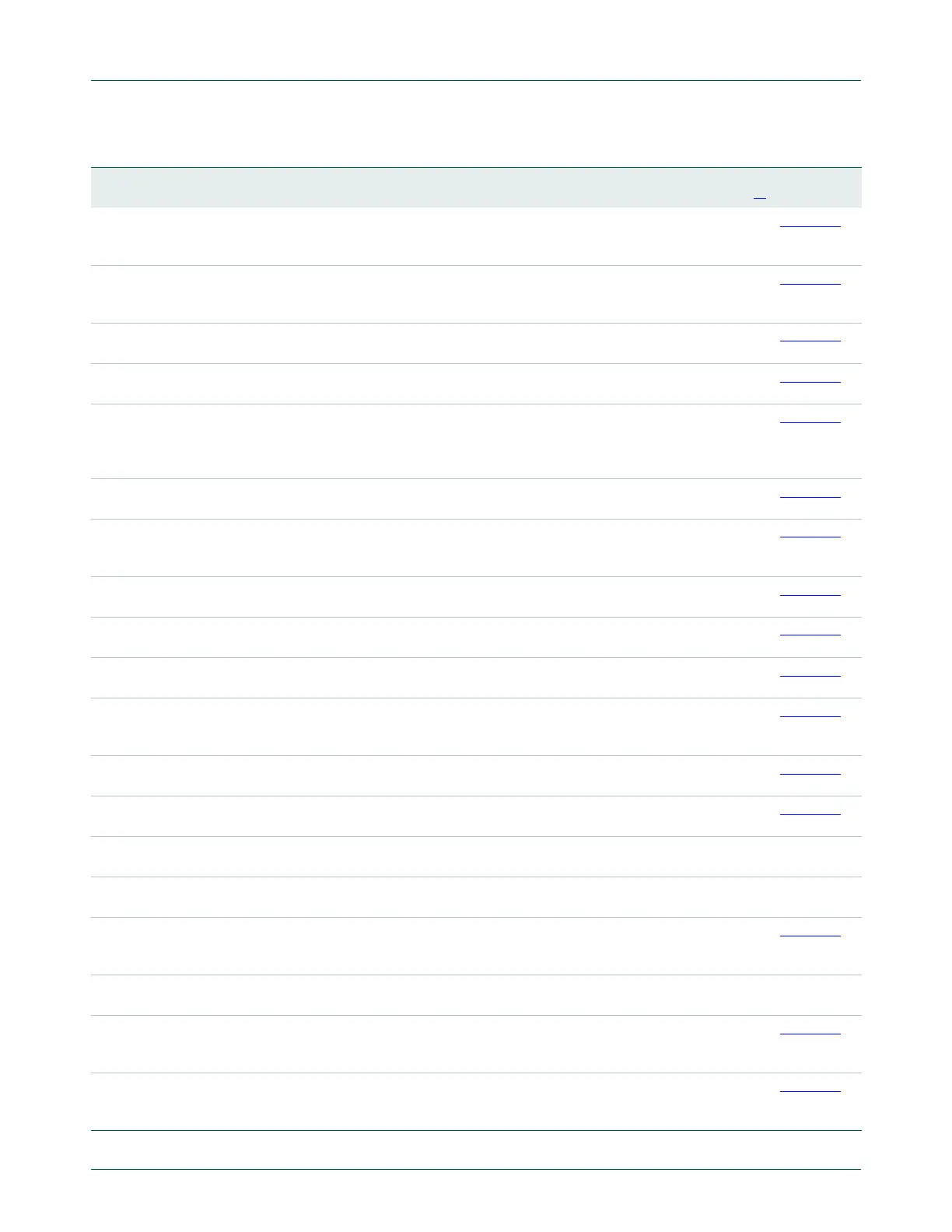

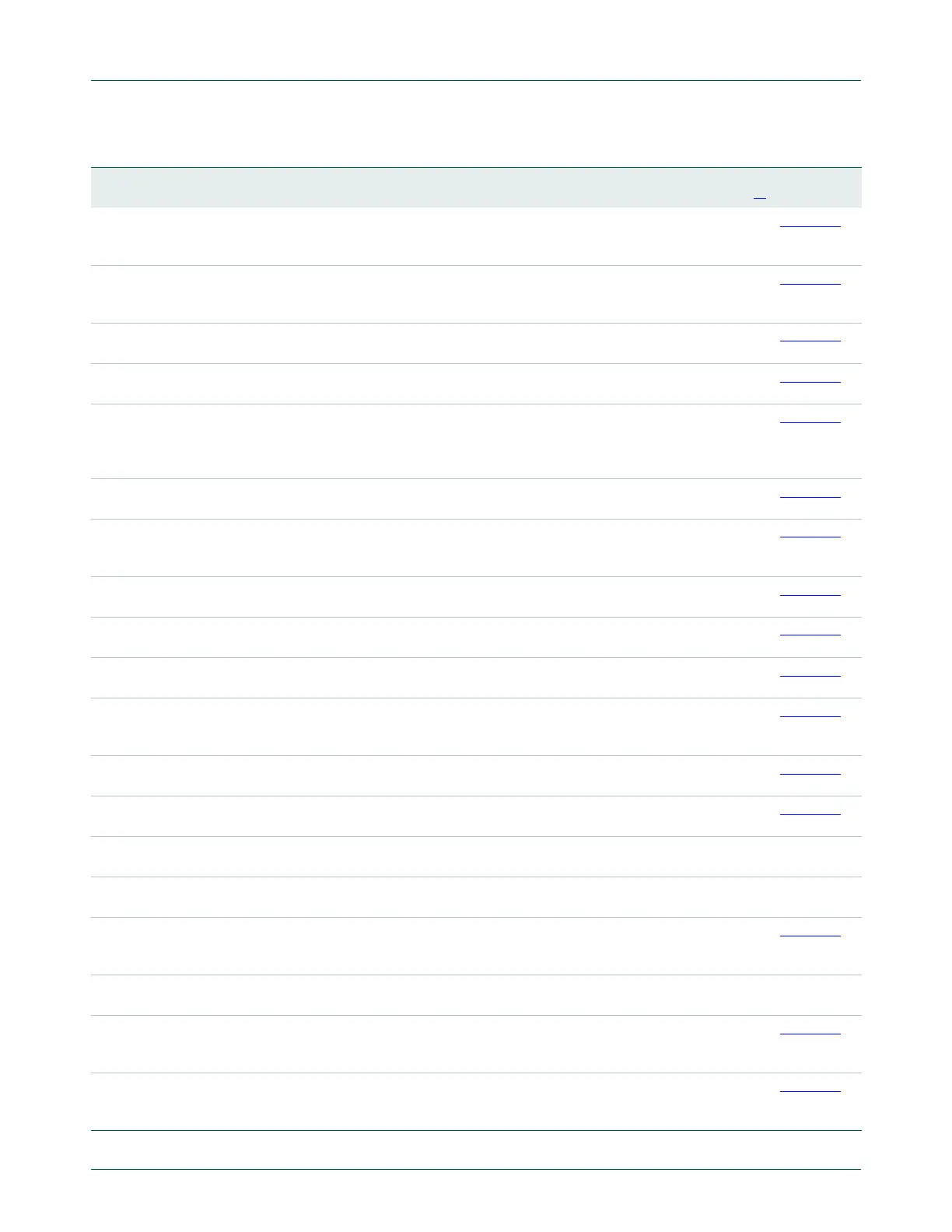

Table 296. Register overview: 16-bit counter/timer 1 CT16B1 (base address 0x4001 0000)

Name Access Address Description Reset

value

[1]

Reference

IR R/W 0x000 Interrupt Register. The IR can be written to clear interrupts. The IR

can be read to identify which of eight possible interrupt sources

are pending.

0 Table 297

TCR R/W 0x004 Timer Control Register. The TCR is used to control the Timer

Counter functions. The Timer Counter can be disabled or reset

through the TCR.

0 Table 299

TC R/W 0x008 Timer Counter. The 16-bit TC is incremented every PR+1 cycles of

PCLK. The TC is controlled through the TCR.

0 Table 300

PR R/W 0x00C Prescale Register. When the Prescale Counter (below) is equal to

this value, the next clock increments the TC and clears the PC.

0 Table 301

PC R/W 0x010 Prescale Counter. The 16-bit PC is a counter which is incremented

to the value stored in PR. When the value in PR is reached, the TC

is incremented and the PC is cleared. The PC is observable and

controllable through the bus interface.

0 Table 302

MCR R/W 0x014 Match Control Register. The MCR is used to control if an interrupt

is generated and if the TC is reset when a Match occurs.

0 Table 303

MR0 R/W 0x018 Match Register 0. MR0 can be enabled through the MCR to reset

the TC, stop both the TC and PC, and/or generate an interrupt

every time MR0 matches the TC.

0 Table 304

MR1 R/W 0x01C Match Register 1. See MR0 description. 0 Table 304

MR2 R/W 0x020 Match Register 2. See MR0 description. 0 Table 304

MR3 R/W 0x024 Match Register 3. See MR0 description. 0 Table 304

CCR R/W 0x028 Capture Control Register. The CCR controls which edges of the

capture inputs are used to load the Capture Registers and whether

or not an interrupt is generated when a capture takes place.

0 Table 305

CR0 RO 0x02C Capture Register 0. CR0 is loaded with the value of TC when there

is an event on the CT16B1_CAP0 input.

0 Table 307

CR1 RO 0x030 Capture Register 1. CR1 is loaded with the value of TC when there

is an event on the CT16B1_CAP1 input.

0 Table 309

- - 0x034 Reserved. - -

- - 0x038 Reserved. - -

EMR R/W 0x03C External Match Register. The EMR controls the match function

and the external match pins CT16B0_MAT[2:0] and

CT16B1_MAT[1:0].

0 Table 310

- - 0x040 -

0x06C

Reserved. - -

CTCR R/W 0x070 Count Control Register. The CTCR selects between Timer and

Counter mode, and in Counter mode selects the signal and

edge(s) for counting.

0 Table 312

PWMC R/W 0x074 PWM Control Register. The PWMCON enables PWM mode for

the external match pins CT16B0_MAT[1:0] and

CT16B1_MAT[1:0].

0 Table 314

Loading...

Loading...