UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 486 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

24.5.2.1 Accessing the Cortex-M0 NVIC registers using CMSIS

CMSIS functions enable software portability between different Cortex-M profile

processors.

To access the NVIC registers when using CMSIS, use the following functions:

[1] The input parameter IRQn is the IRQ number, see Table 421 for more information.

24.5.2.2 Interrupt Set-enable Register

The ISER enables interrupts, and shows which interrupts are enabled. See the register

summary in Table 434

for the register attributes.

The bit assignments are:

If a pending interrupt is enabled, the NVIC activates the interrupt based on its priority. If an

interrupt is not enabled, asserting its interrupt signal changes the interrupt state to

pending, but the NVIC never activates the interrupt, regardless of its priority.

24.5.2.3 Interrupt Clear-enable Register

The ICER disables interrupts, and show which interrupts are enabled. See the register

summary in Table 24–434

for the register attributes.

The bit assignments are:

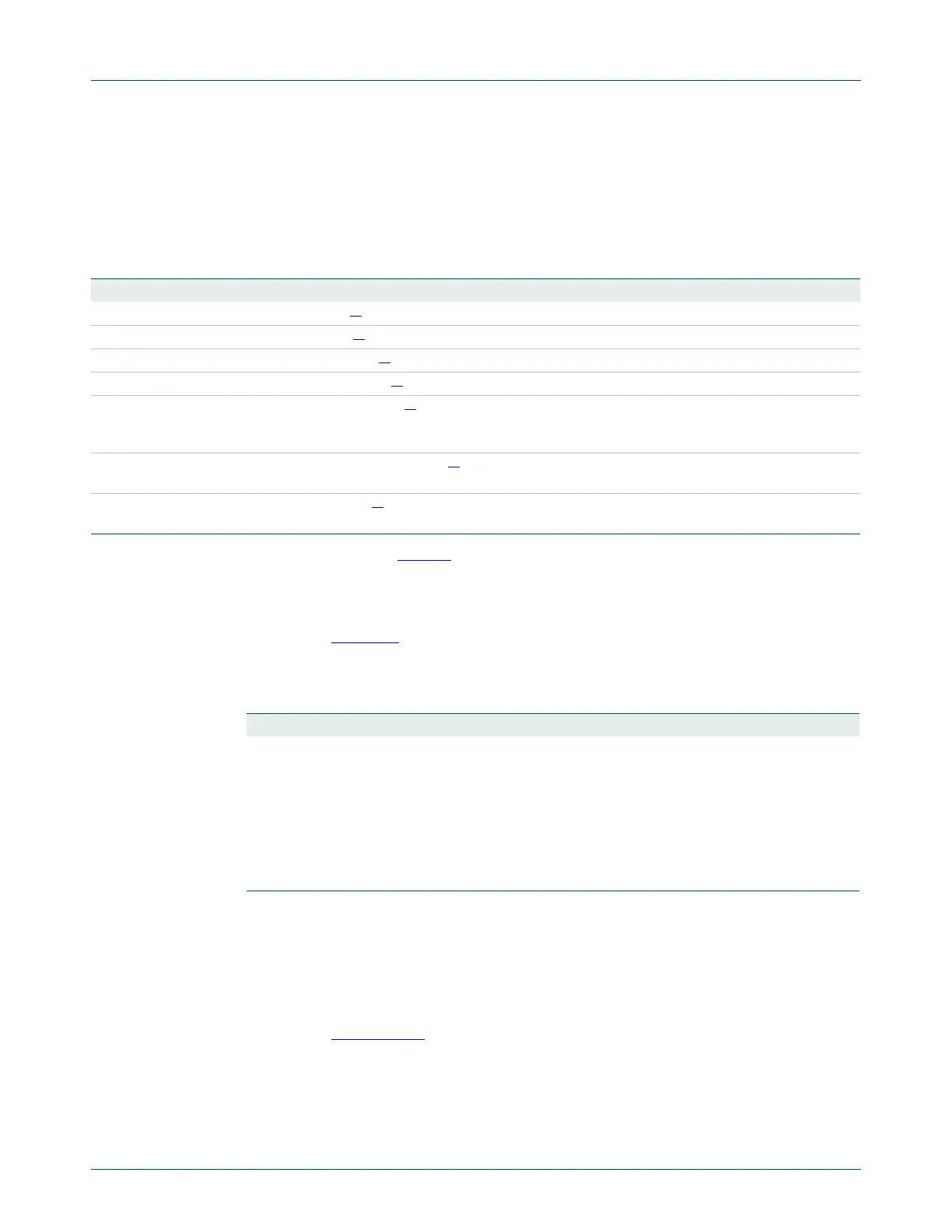

Table 435. CMISIS acess NVIC functions

CMSIS function Description

void NVIC_EnableIRQ(IRQn_Type IRQn)

[1]

Enables an interrupt or exception.

void NVIC_DisableIRQ(IRQn_Type IRQn)

[1]

Disables an interrupt or exception.

void NVIC_SetPendingIRQ(IRQn_Type IRQn)

[1]

Sets the pending status of interrupt or exception to 1.

void NVIC_ClearPendingIRQ(IRQn_Type IRQn)

[1]

Clears the pending status of interrupt or exception to 0.

uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn)

[1]

Reads the pending status of interrupt or exception.

This function returns non-zero value if the pending status is set

to 1.

void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority)

[1]

Sets the priority of an interrupt or exception with configurable

priority level to 1.

uint32_t NVIC_GetPriority(IRQn_Type IRQn)

[1]

Reads the priority of an interrupt or exception with configurable

priority level. This function returns the current priority level.

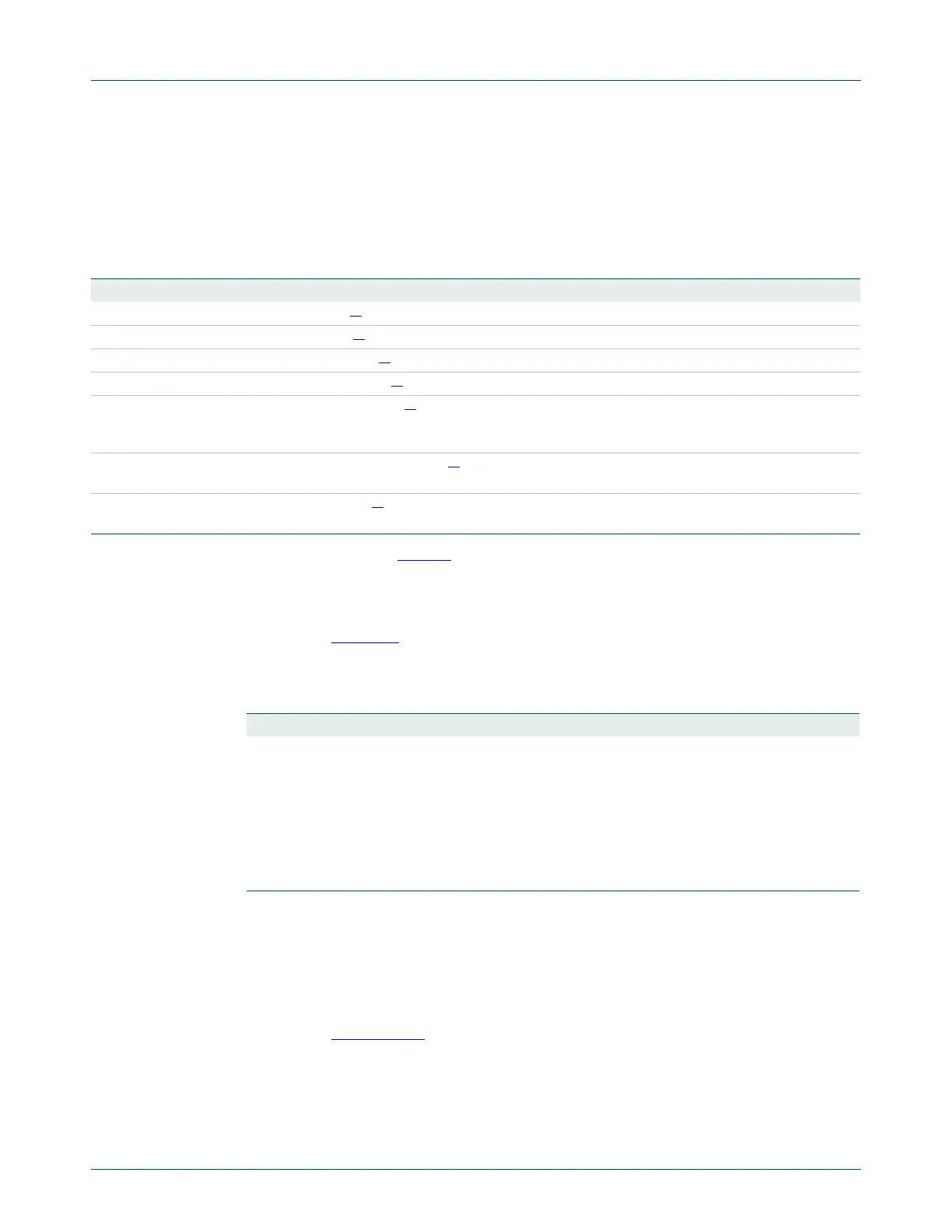

Table 436. ISER bit assignments

Bits Name Function

[31:0] SETENA Interrupt set-enable bits.

Write:

0 = no effect

1 = enable interrupt.

Read:

0 = interrupt disabled

1 = interrupt enabled.

Loading...

Loading...