UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 485 of 523

NXP Semiconductors

UM10462

Chapter 24: LPC11U3x/2x/1x Appendix ARM Cortex-M0

24.4.7.12.5 Examples

WFI ; Wait for interrupt

24.5 Peripherals

24.5.1 About the ARM Cortex-M0

The address map of the Private peripheral bus (PPB) is:

In register descriptions, the register type is described as follows:

RW — Read and write.

RO — Read-only.

WO — Write-only.

24.5.2 Nested Vectored Interrupt Controller

This section describes the Nested Vectored Interrupt Controller (NVIC) and the

registers it uses. The NVIC supports:

• 32 interrupts.

• A programmable priority level of 0-3 for each interrupt. A higher level corresponds to a

lower priority, so level 0 is the highest interrupt priority.

• Level and pulse detection of interrupt signals.

• Interrupt tail-chaining.

• An external Non-maskable interrupt (NMI).

The processor automatically stacks its state on exception entry and unstacks this state on

exception exit, with no instruction overhead. This provides low latency exception handling.

The hardware implementation of the NVIC registers is:

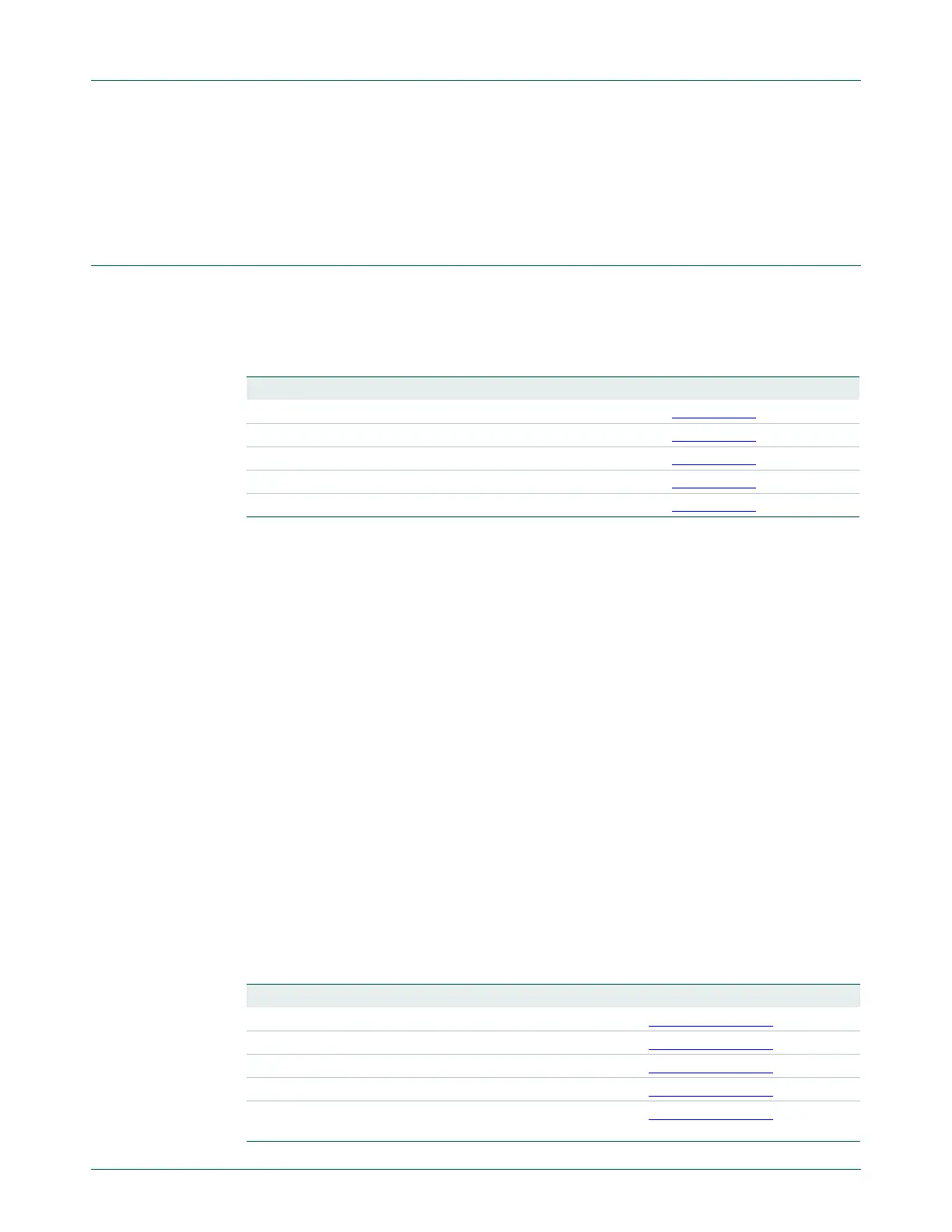

Table 433. Core peripheral register regions

Address Core peripheral Description

0xE000E008

-

0xE000E00F

System Control Block Table 24–442

0xE000E010

-

0xE000E01F

System timer Table 24–451

0xE000E100

-

0xE000E4EF

Nested Vectored Interrupt Controller Table 24–434

0xE000ED00

-

0xE000ED3F

System Control Block Table 24–442

0xE000EF00

-

0xE000EF03

Nested Vectored Interrupt Controller Table 24–434

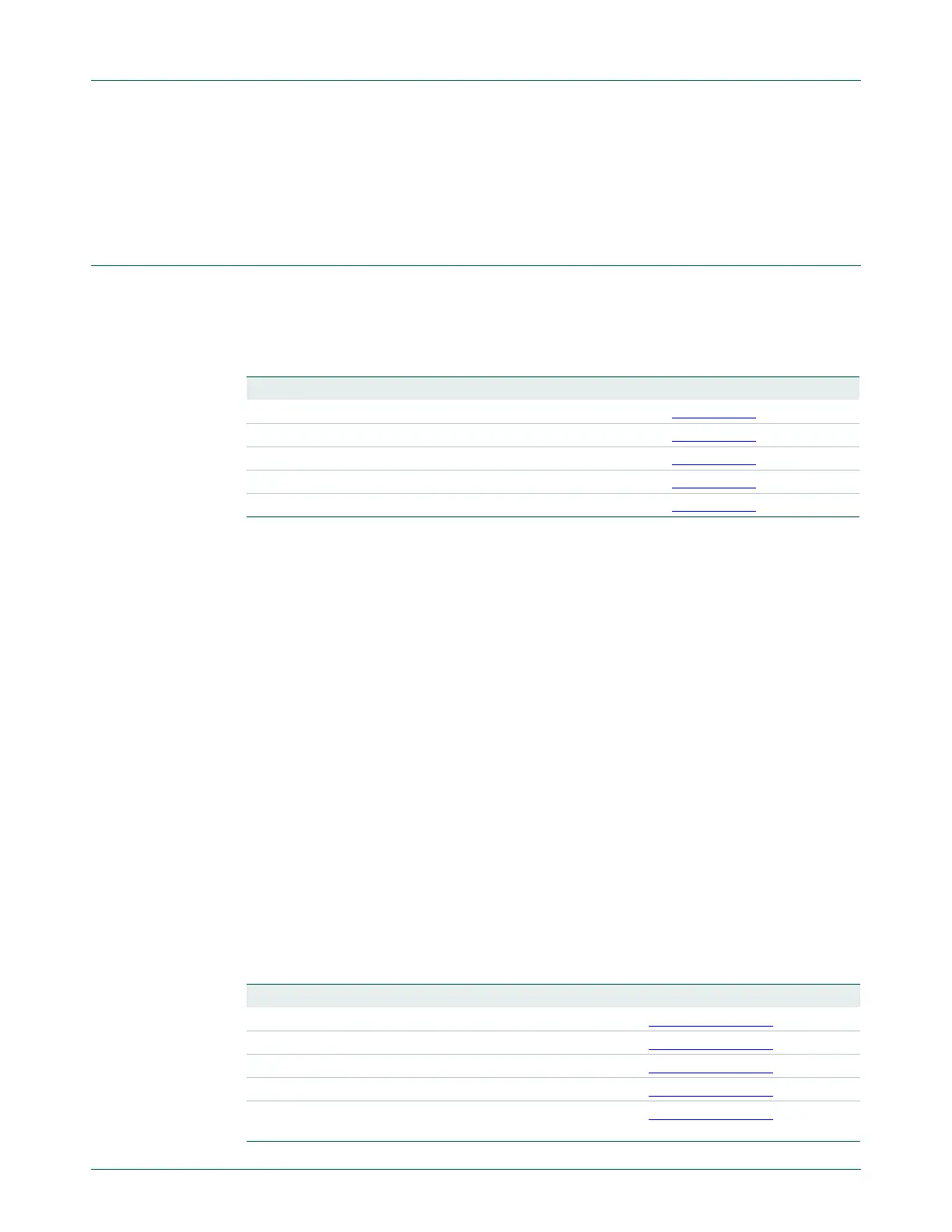

Table 434. NVIC register summary

Address Name Type Reset value Description

0xE000E100

ISER RW

0x00000000

Section 24–24.5.2.2

0xE000E180

ICER RW

0x00000000

Section 24–24.5.2.3

0xE000E200

ISPR RW

0x00000000

Section 24–24.5.2.4

0xE000E280

ICPR RW

0x00000000

Section 24–24.5.2.5

0xE000E400

-

0xE

000E41C

IPR0-7 RW

0x00000000

Section 24–24.5.2.6

Loading...

Loading...