Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 107

UG366 (v2.5) January 17, 2011

Reference Clock Selection

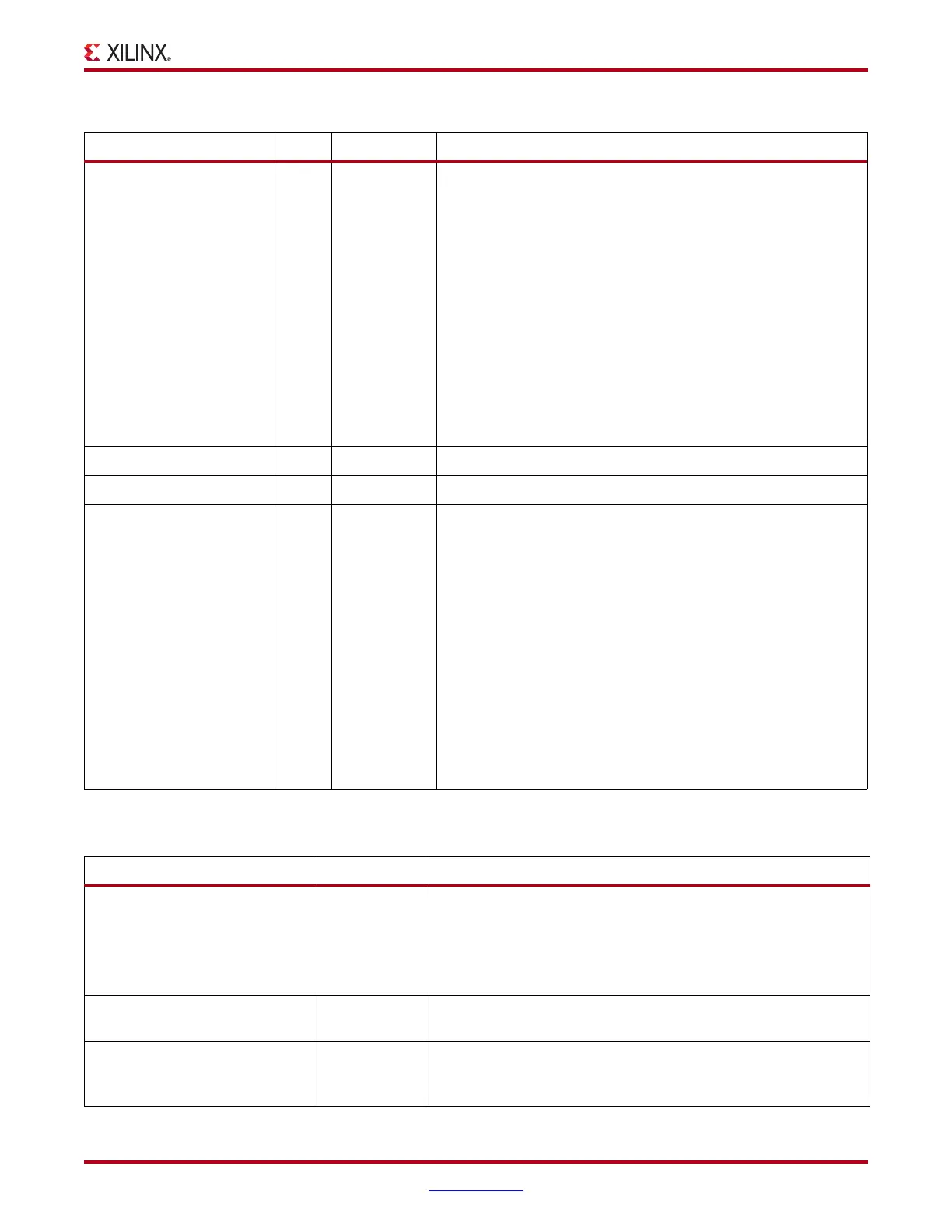

Table 2-5 defines the GTX clocking attributes.

RXPLLREFSELDY[2:0] In Async Receiver PLL reference clock dynamic selection. Set to 000 when

one reference clock is used.

When multiple reference clocks are connected,

RXPLLREFSELDY provides dynamic selection as follows:

000: MGTREFCLKRX[0] selected

001: MGTREFCLKRX[1] selected

010: NORTHREFCLKRX[0] selected

011: NORTHREFCLKRX[1] selected

100: SOUTHREFCLKRX[0] selected

101: SOUTHREFCLKRX[1] selected

110: No connect

111: GREFCLKRX or PERFCLKRX selected (only one of these

can be used at a time)

SOUTHREFCLKRX[1:0] In Clock South-bound clocks from the Quad above.

SOUTHREFCLKTX[1:0] In Clock South-bound clocks from the Quad above.

TXPLLREFSELDY[2:0] In Async Transmitter PLL reference clock dynamic selection. Set to 000

when one reference clock is used.

When multiple reference clocks are connected,

TXPLLREFSELDY provides dynamic selection as follows:

000: MGTREFCLKTX[0] selected

001: MGTREFCLKTX[1] selected

010: NORTHREFCLKTX[0] selected

011: NORTHREFCLKTX[1] selected

100: SOUTHREFCLKTX[0] selected

101: SOUTHREFCLKTX[1] selected

110: CAS_CLK (Internal clock generated from the RX PLL)

111: GREFCLKTX or PERFCLKTX selected (only one of these

can be used at a time)

Table 2-4: GTX Clocking Ports (Cont’d)

Port Dir Clock Domain Description

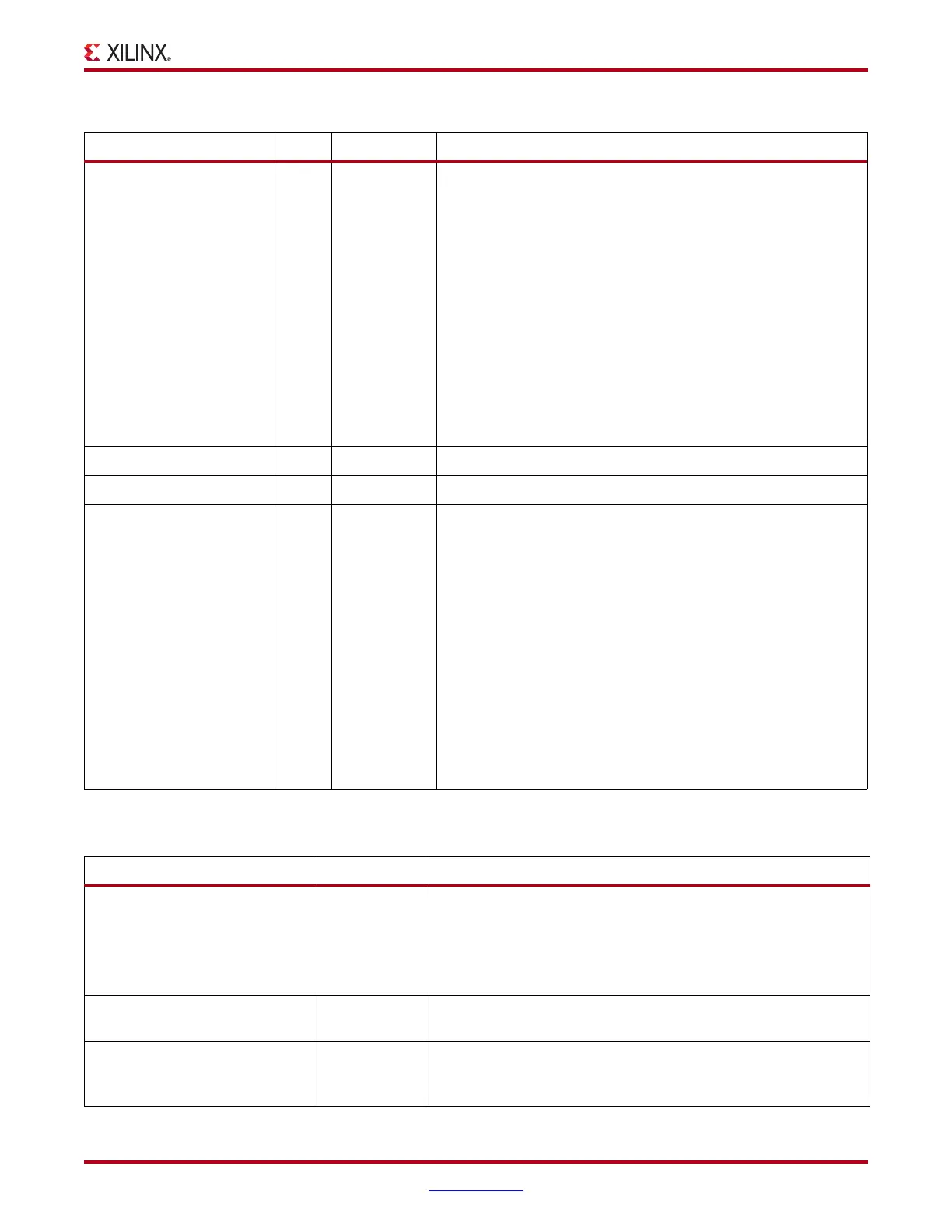

Table 2-5: GTX Clocking Attributes

Attribute Type Description

PMA_CAS_CLK_EN Boolean This attribute is the enable for CAS_CLK from the receiver

forwarded to the transmitter PLL.

TRUE: Enables CAS_CLK. TXPLLREFSELDY[2:0] is unused in

this case.

FALSE: Disables CAS_CLK.

SIM_RXREFCLK_SOURCE[2:0] 3-bit Binary Simulation control for GTX reference clock selection. This attribute

must contain the same binary value as the RXPLLREFSELDY port.

SIM_TXREFCLK_SOURCE[2:0] 3-bit Binary Simulation control for the GTX reference clock selection. This

attribute is set to the same binary value as the TXPLLREFSELDY

port.

Loading...

Loading...