Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 141

UG366 (v2.5) January 17, 2011

TX Initialization

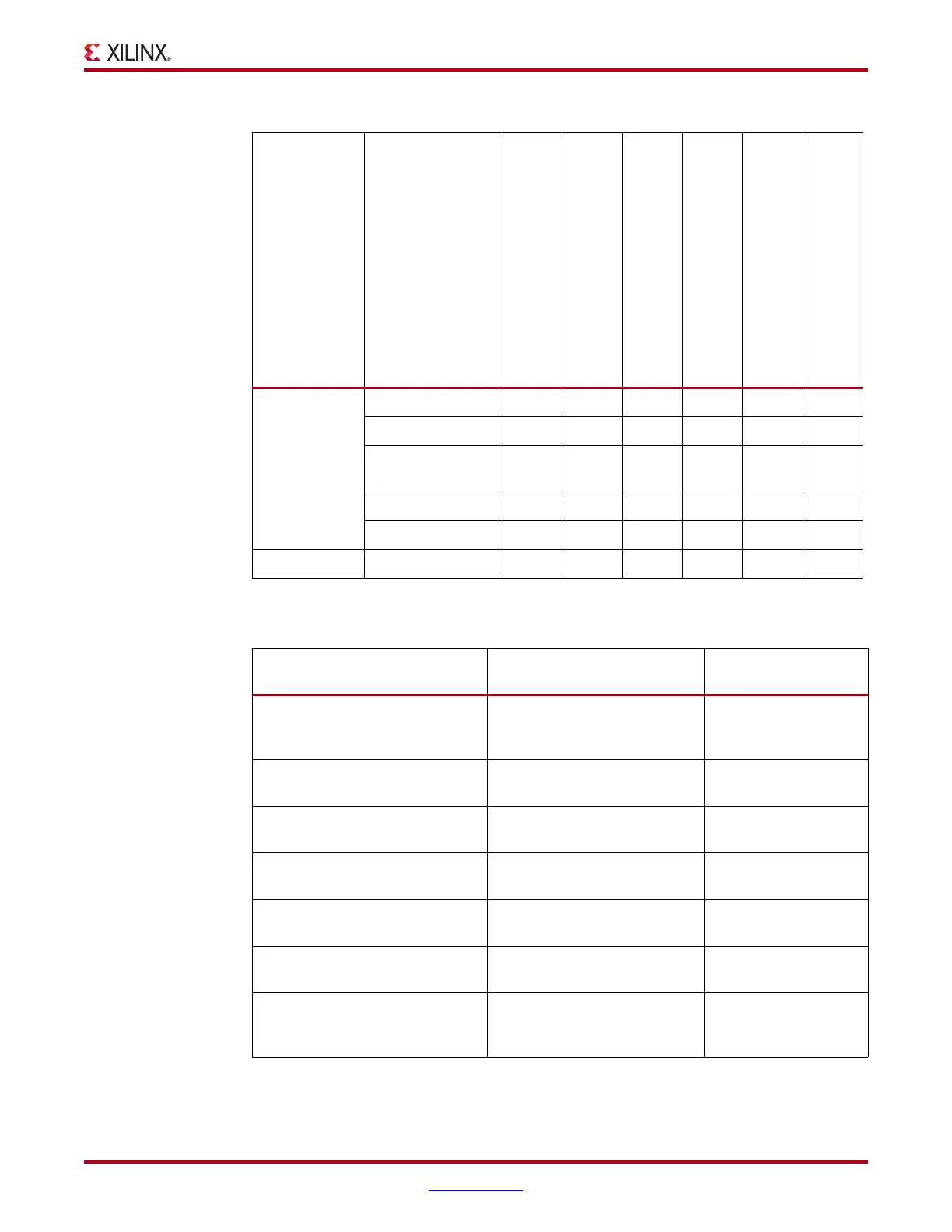

Table 3-10 lists the recommended resets for various situations.

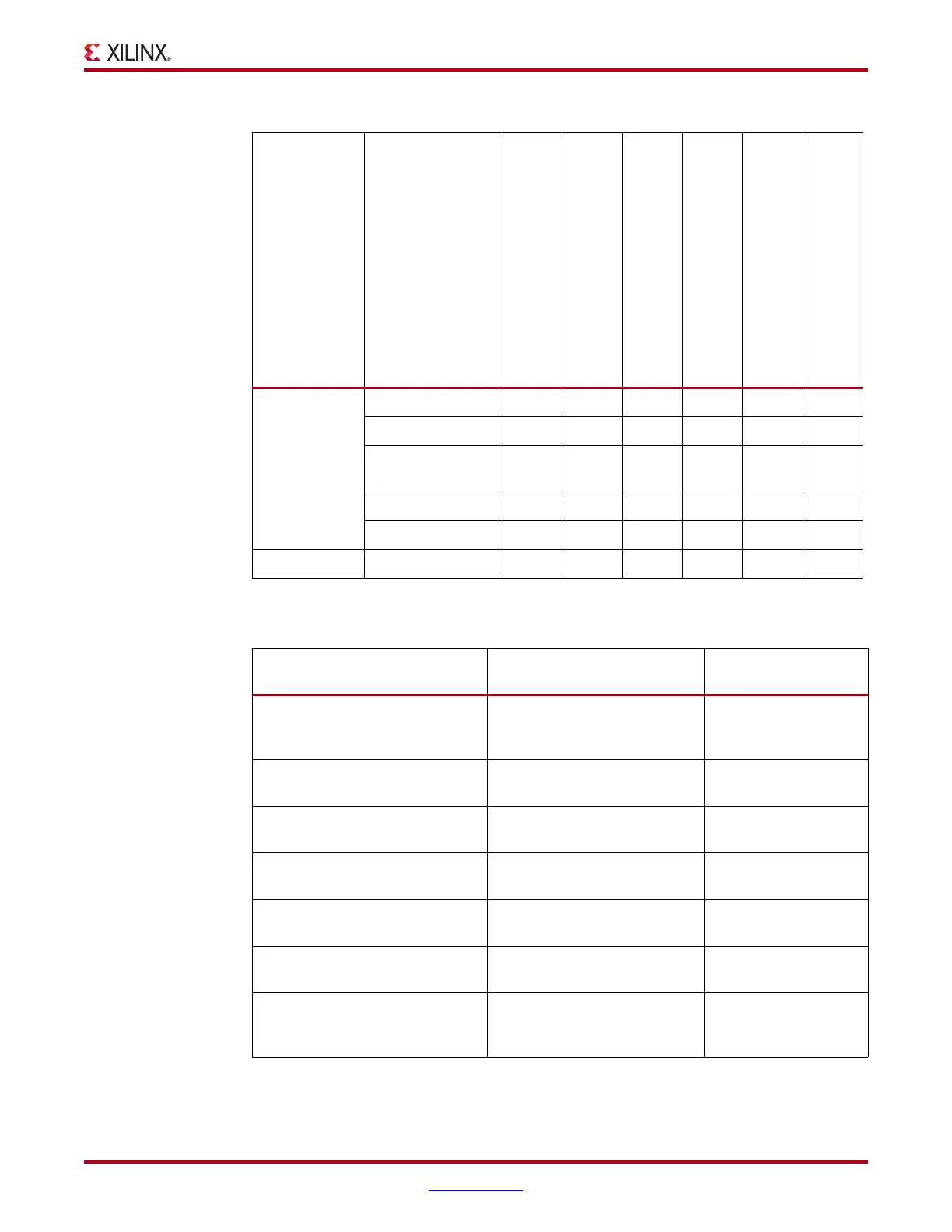

TX PMA

TX Driver ✓✓✓

TX OOB ✓✓✓

TX Receiver Detect

for PCIe Designs

✓✓✓

TX PLL ✓✓✓✓

PISO ✓✓✓

Loopback Loopback Paths ✓✓✓

Table 3-10: Recommended Resets for Common Situations

Situation Components to be Reset

Recommended

Reset

(1)

After power up and configuration Entire GTX TX

After configuration,

GTX TX is reset

automatically

After turning on a reference clock

to the TX PLL

Entire GTX TX GTXTXRESET

After changing the reference clock

to the TX PLL

Entire GTX TX GTXTXRESET

After assertion/deassertion of

TXPOWERDOWN

Entire GTX TX GTXTXRESET

TX rate change with the TX buffer

bypassed

TX PCS, TX Phase Alignment

GTXTEST[1],

TXRESET

TX rate change with TX buffer

enabled

TX PLL Output Clock Dividers,

TX PCS

GTXTEST[1],

TXRESET

TX parallel clock source reset

TX PLL Output Clock Dividers,

TX Delay Aligner, TX Phase

Alignment, TX PCS

GTXTEST[1],

TXDLYALIGNRESET,

TXRESET

Notes:

1. The recommended reset has the smallest impact on the other components of the GTX transceiver.

Table 3-9: Available Transmitter Resets and the Components Reset by Them

Component

Configuration

GTXTXRESET

TXPLLPOWERDOWN (Falling Edge)

PLLTXRESET

TXRESET

TXDLYALIGNRESET

Loading...

Loading...