150 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

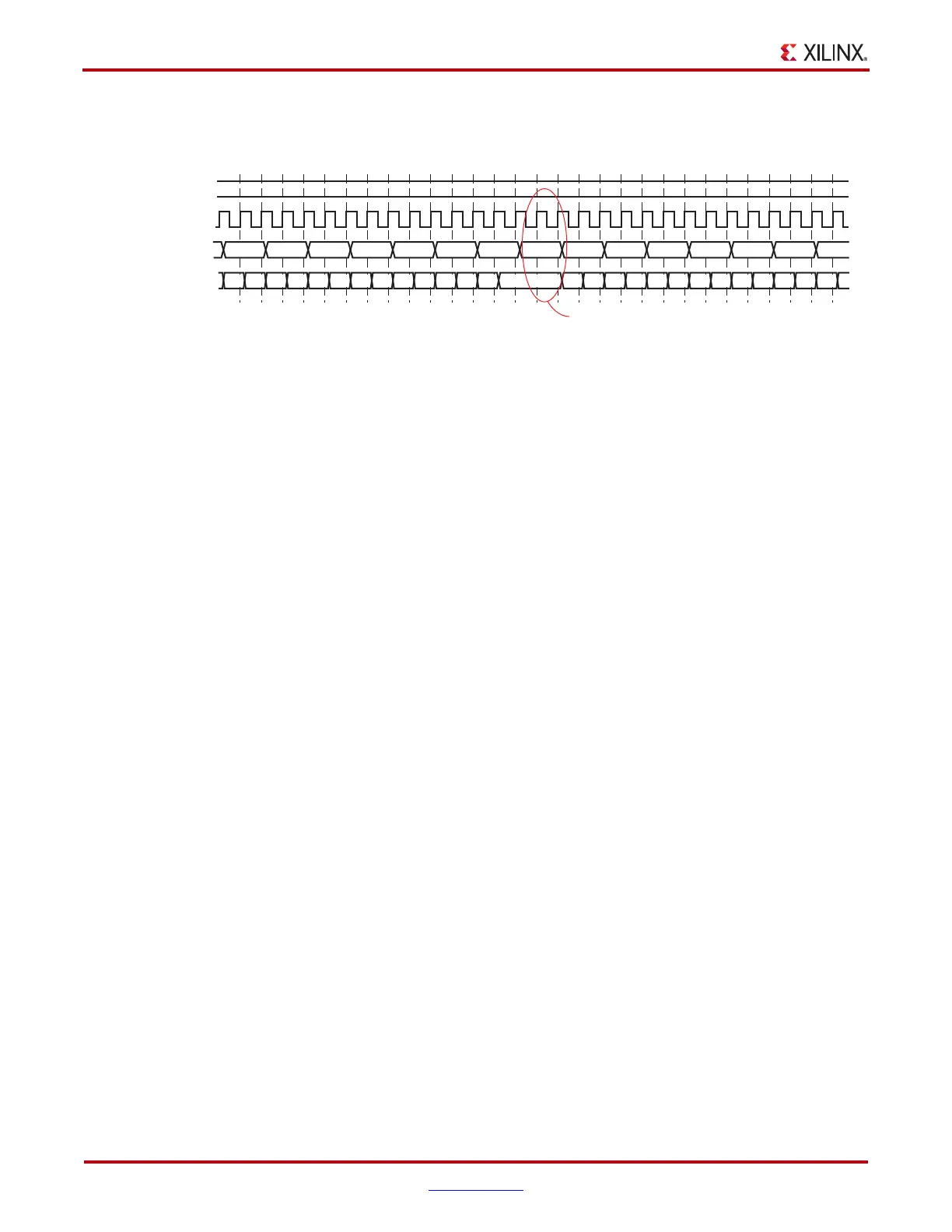

Figure 3-16 shows how a pause occurs at counter value 44 when using a 2-byte interface,

external sequence counter mode, and 64B/67B encoding.

The sequence of transmitting 64B/67B data for the external sequence counter mode is:

1. Assert TXRESET and wait until the reset cycle is completed.

2. During reset, drive 7'h00 on TXSEQUENCE, header information on

TXHEADER[2:0], and initial data on TXDATA. This state can be held indefinitely in

readiness for data transmission.

3. On count 0, drive data to TXDATA and header information to TXHEADER. For a

2-byte interface, drive a second 2 bytes to TXDATA while still on count 0.

4. The sequence counter increments to 1 while driving data on TXDATA.

5. After applying 4 bytes of data, the counter increments to 2 and drives data on TXDATA

and header information on TXHEADER[2:0].

6. On count 21, stop the data pipeline.

7. On count 22, drive data on TXDATA.

8. On count 44, stop the data pipeline.

9. On count 45, drive data on TXDATA.

10. On count 65, stop the data pipeline.

11. On count 66, drive data on TXDATA.

The sequence of transmitting 64B/66B data for the external sequence counter mode is:

1. Assert TXRESET and wait until the reset cycle is completed.

2. During reset, drive 6'h00 on TXSEQUENCE, header information on

TXHEADER[1:0], and initial data on TXDATA. This state can be held indefinitely in

readiness for data transmission.

3. On count 0, drive data to TXDATA and header information to TXHEADER[1:0]. For a

2-byte interface, drive a second 2 bytes to TXDATA while still on count 0.

4. The sequence counter increments to 1 while driving data on TXDATA.

5. After applying 4 bytes of data, the counter increments to 2 and drives data on TXDATA

and header information on TXHEADER.

6. On count 31, stop the data pipeline.

7. On count 32, drive data on TXDATA.

X-Ref Target - Figure 3-16

Figure 3-16: Pause at Sequence Counter Value 44

-

TXHEADER0

TXUSRCLK20

TXSEQUENCE0

TXDATA0

UG366_c3_06_051509

Pause for 2 USRCLK2 cycles. Data is ignored.

1

37

10ea 79e6 d48c c995 c9ec 651c 1921 2751 119e 3475 98e9 2043 87c7 a738c5d4aaeb 2467 0959 aced 0509 0e26 0646 0996 812a e700 b320 6859

38 3940414243 44 45 46 47 48 49 50 51

Loading...

Loading...