174 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

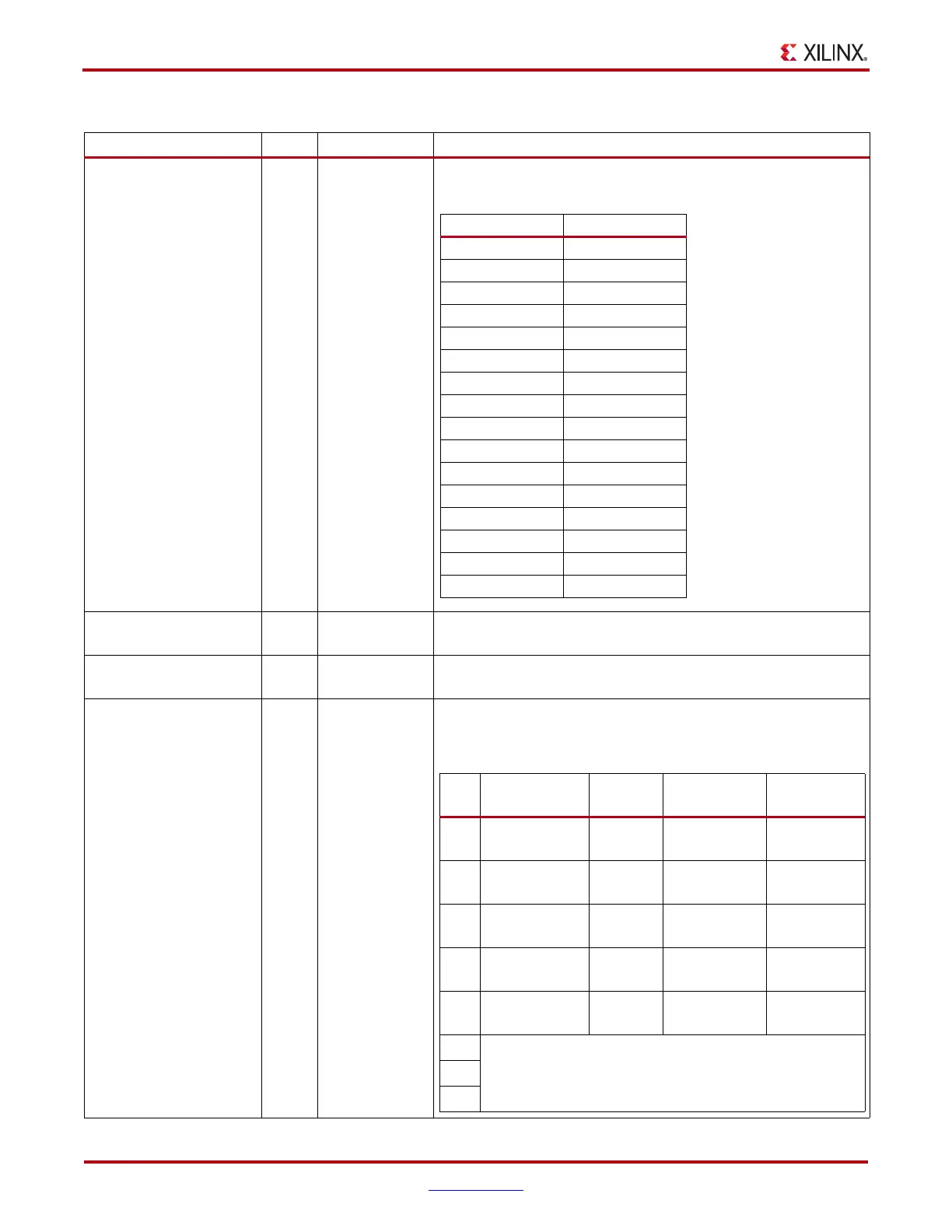

TXDIFFCTRL[3:0] In Async Driver Swing Control. The default is user specified. All listed

values (mV

PPD

) are typical.

TXELECIDLE In TXUSRCLK2,

Async

TXPDOWNASYNCH makes this pin asynchronous.

TXINHIBIT In TXUSRCLK2 When High, this signal blocks transmission of TXDATA and

forces TXP to 0 and TXN to 1.

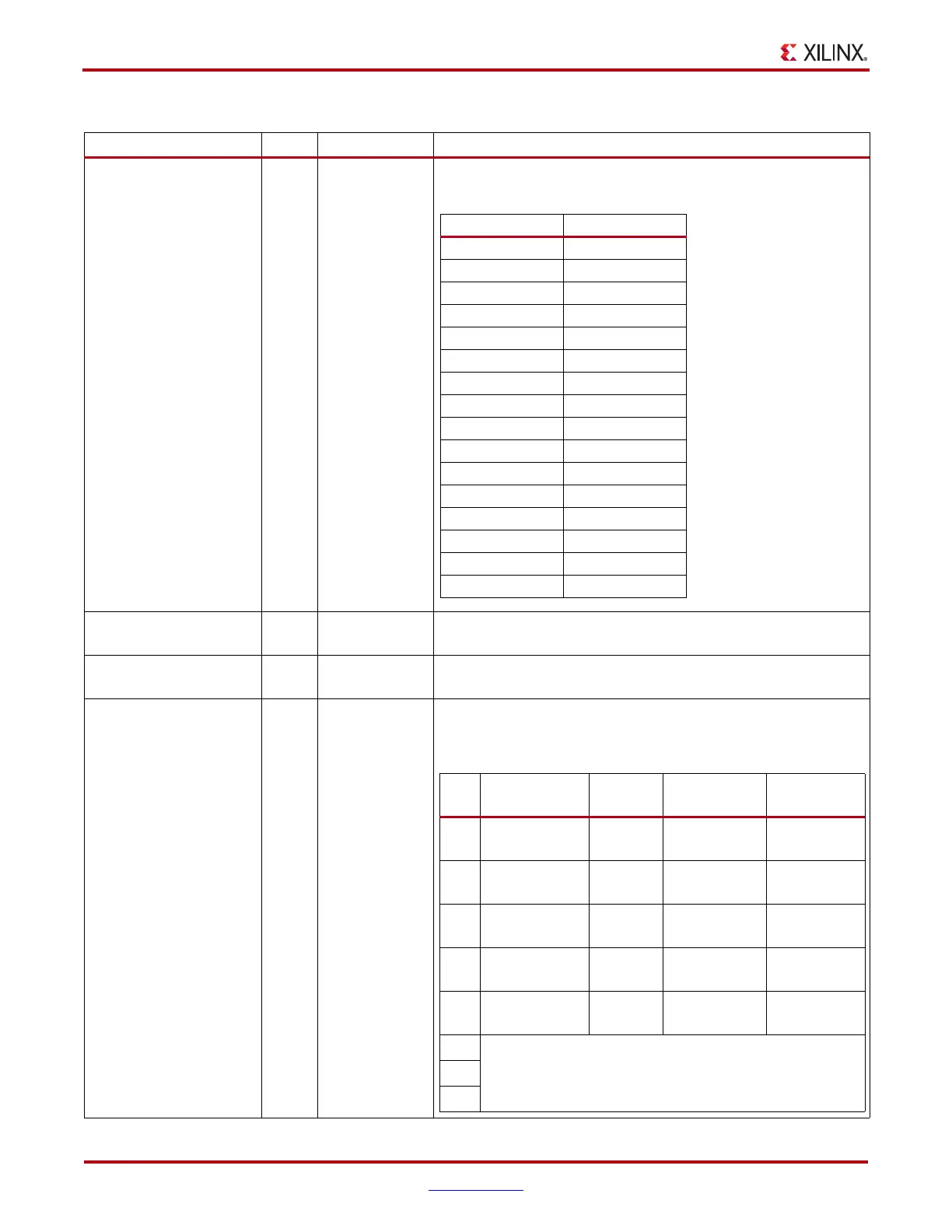

TXMARGIN[2:0] In Async TX Margin control for PCI Express PIPE Interface

(1)

. These signals

are mapped internally to TXDIFFCTRL/TXBUFDIFFCTRL via

attributes.

Table 3-31: TX Configurable Driver Ports (Cont’d)

Port Dir Clock Domain Description

[3:0] mV

PPD

0000 110

0001 210

0010 310

0011 400

0100 480

0101 570

0110 660

0111 740

1000 810

1001 880

1010 940

1011 990

1100 1040

1101 1080

1110 1110

1111 1130

[2:0] Full Range Half Range

Full Range

Attribute

Half Range

Attribute

000 800-1200 400-1200

TX_MARGIN_

FULL_0

TX_MARGIN_

LOW_0

001 800-1200 400-700

TX_MARGIN_

FULL_1

TX_MARGIN_

LOW_1

010 800-1200 400-700

TX_MARGIN_

FULL_2

TX_MARGIN_

LOW_2

011 200-400 100-200

TX_MARGIN_

FULL_3

TX_MARGIN_

LOW_3

100 100-200 100-200

TX_MARGIN_

FULL_4

TX_MARGIN_

LOW_4

101

default to “DIRECT” mode110

111

Loading...

Loading...